一文读懂异构多处理系统-一个异构多处理系统由不同类型的多个单核心或多核心处理器构成,异构多核处理系统最简单的形式是由一个多核处理器和GPU组成。然而,现代科技让一颗芯片上的异构多处理系统包含以下模块。

采用WISHBONE总线有效地解决IP核可移植性、设计复用问题-清华大学嵌入式微处理器芯片设计为国家重点863项目,单芯片多处理器设计为项目的一个延伸。单芯片多处理器是提高处理器性能的有效途径,具有低耦合度、粗粒度并行性的主要特点。清华大学已成功开发出具有自主知识产权的MIPS 4Kc架构的32位微处理器–THUMPl07。该处理器具有内核性能高、面积小、功耗低的优点。使其经过裁减非常适合作为单芯片多处理器的内核。

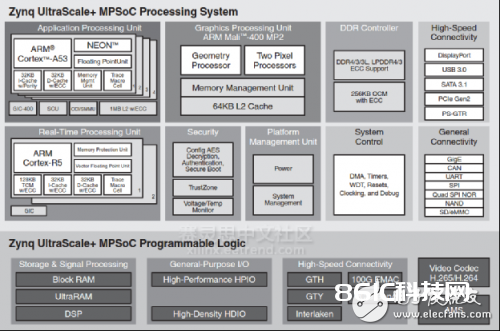

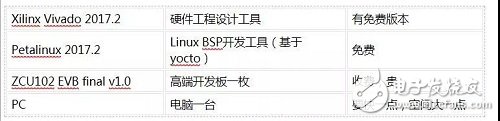

Zynq UltraScale+ MPSoC 上的多个Linux UIO设计-本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

;多处理器通信的写法分析;学习多处理通信的接收程序ADDREQU27HSTOPEQU00H;ORG0000HRESTE:MOVR0,#00HL0:DJNZR0,L0;START:LCALLINIT_S

处理器速度如何提升推动40GbE向前发展?-服务器CPU处理速度的提升,加上支持多处理器核心的芯片出现,都会不断地提升服务器的计算能力。此外,虚拟化加大了服务器实际可用功能的碎片化。这些因素可以提升各