工程师设计经验分享:画FPGA开发板所犯的那些错误-这里先截下我最初画这个开发板的一张惨不忍睹的PCB让大家看看。TopLayer如图: BottomLayer如图: 第一遍画的时候,想速战速决把它画完,草草了事,但是等全部布线完以后却发现这里面的错误实在是太多了,我觉得最核心的错误就是一开始就没有注意整个系统各个元器件的布局,从而导致了灾难的发生,后来的布线也就非常困难。大家很容易可以在上图中看出布线的长度大部分都很长,其实这也是非常严重的错误,尤其对于高速信号线来说。输入、输出

利用FPGA开发的太阳能自动跟踪系统设计-当时间为正常光照时间时,太阳跟踪系统每隔5 min就会进入太阳高度角方位角进行计算。计时模块输出给太阳高度角方位角模块所需的时间信息,然后计算赤道坐标系下的赤纬角和时角,最后计算高度角方位角坐标系下的高度角和方位角值,并输出高度角和方位角值如图6所示,仿真波形如图7所示。高度角和方位角输出均为10 b Q7格式。

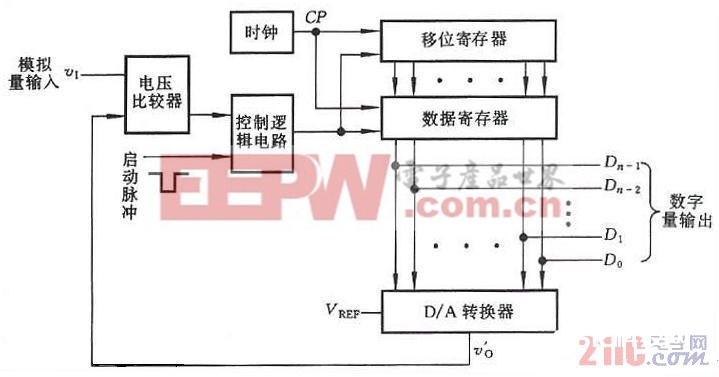

ADC 逐次比较型1.转换方式直接转换ADC2.电路结构逐次逼近ADC包括n位逐次比较型A/D转换器如图11.10.1所示。它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。 图