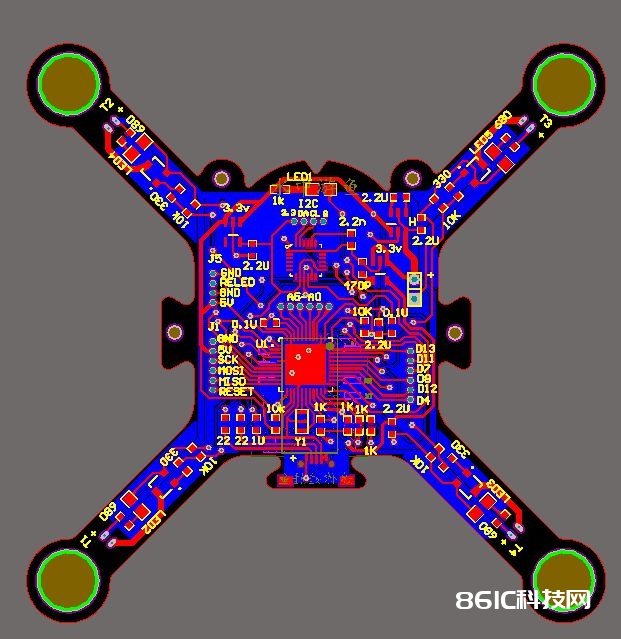

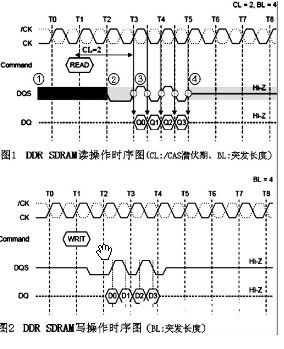

提高信号完整性、减小串扰和反射是高速电路系统设计能否成功的关键。本文基于以ARM1176JZF-S S3C6410为核处理器的嵌入式开发系统,对高速电路进行了研究。通过信号完整性仿真分析,解决了DDR

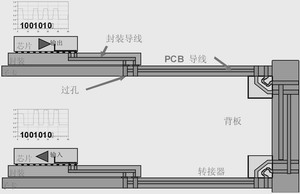

基于信号完整性分析的PCB设计流程如图所示。主要包含以下步骤:图基于信号完整性分析的高速PCB设计流程(1)因为整个设计流程是基于信号完整性分析的,所以在进行PCB设计之前,必须建立或获取高速数字信号

随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成为传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具和互连工具可以帮助设计设计师解决部分难题