关于STM32配置中断和GPIO针脚问题-嵌入式软体搭配最新版的STM32CubeMX个人电 脑开发 工具使用, 设计人员 可在绘图介面向导内配置微控制器,只要按一下,即可生成初始化C代码,直接用於多款市面上流行的 第三方开发 工具。

如何破解单片机解密芯片-单片机加解密可划分为两大类,一类是硬件加解密,一类是软件加解密。硬件加密,对于单片机来说,一般是单片机厂商将加密熔丝固化在IC内,熔丝有加密状态及不加密状态,如果处于加密状态,一般的工具是读取不了IC里面的程序内容的,要读取其内容,这就涉及到硬件解密,必须有专业的硬件解密工具及专业的工程师。

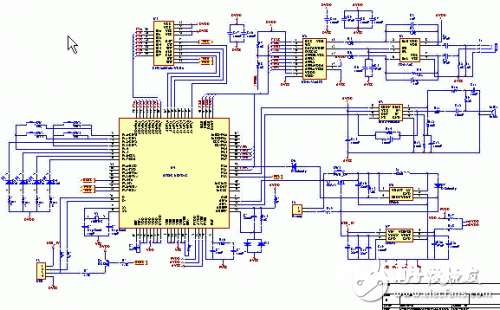

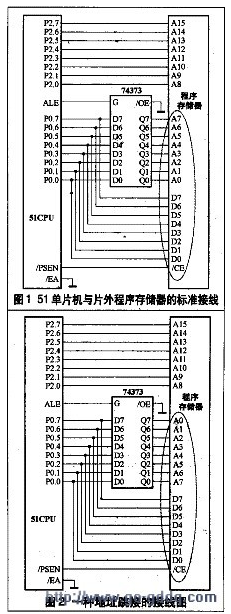

如何实现单片机程序代码的反汇编-要进行目标代码的变换,首先必须根据硬件画出实际的地址和数据的接线图,然后借助于工具软件进行变换。在“51汇编集成开发环境”(其下载网址为www1.skycn.com/SOFt/15074/html)中,提供了一个变换工具,从软件界面的[辅助工具]—[目标代码转换]-[bin代码还原]就可以启动这个工具。

FPGA开发流程详细解析-1. FPGA 开发流程: 电路设计与设计输入 ;仿真验证:利用Xilinx集成的仿真工具足矣 ;逻辑综合:利用XST(Xilinx Synthesis Tool)工具 ;布局布线:利用Xilinx的Implementation Tool工具 ;FPGA配置下载:利用iMPACT工具 2. 时序标注文件是指SDF(Standard Delay Format Timing Annotation)文件,在Xilinx公司的FPGA/CPLD设计中使用“.sdf”作为时序标注文件的扩展名,而在 Altera 公司的FPGA设计中使用“.sdo”作为时序标注文件的扩展名。

FPGA开发中的脚本语言有哪些?-多数FPGA开发者都习惯图形化界面(GUI)。GUI方式简单易学,为小项目提供了一键式流程。然而,随着FPGA项目越来越复杂,在很多情况下GUI工具就阻碍了工作效率。因为GUI工具不能对整个开发过程提供足够的灵活性和控制。另一方,GUI工具本身会占用很大一部CPU资源和内存。

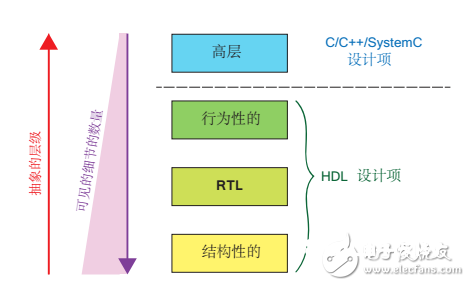

FPGA设计工具的重要性 DSP设计基本流程-在摩尔定律的作用下,FPGA产品的门数量不断增加,性能与专门功能逐渐加强,使得FPGA在电子系统领域能够取代此前只有ASIC和ASSP才能发挥的作用。不过,说到底,FPGA必须要有适当的设计工具辅助,让设计人员充分发挥其作用,否则再好的产品也毫无意义。

FPGA设计中的HLS 工具应用-在集成电路行业飞速发展的今天,缩短产品开发的周期而又不牺牲验证过程,这不可避免地成为了商业市场的一个关键因素。Xilinx Vivado High Level Synthesis (即Vivado HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。