半导体工艺的良品率测量点-维持及提高工艺和产品的良品率对半导体工艺至关重要。任何对半导体工业做过些许了解的人都会发现,整个工艺对其生产良品率极其关注。的确如此,半导体制造工艺的复杂性,以及生产一个完整封装器件所需要经历的庞大工艺制程数量,是导致这种对良品率的关注超乎寻常的基本原因。

半导体制造去除氧化层的方法-理想的清洗工艺是应用那些完全安全、易于并比较经济地进行处理的化学品,并且在室温下进行,这种工艺并不存在。然而,关于室温下化学反应的研究正在进行。其中一种是将臭氧与另外两种浓度的氢氟酸溶液在室温下注入盛有超纯净水的清洗池。兆赫兹超声波作为辅助以提高清洗的有效性。

STC12C5A60S2单片机的内部构造及功能详细介绍-STC12C5A60S2单片机是一款功能比较强大的单片机,在众多的51系列单片机中,要算国内STC 公司的1T增强系列更具有竞争力,因他不但和8051指令、管脚完全兼容,而且其片内的具有大容量程序存储器且是FLASH工艺的,如STC12C5A60S2单片机内部就自带高达60K FLASH ROM,这种工艺的存储器用户可以用电的方式瞬间擦除、改写。而且STC系列单片机支持串口程序烧写。

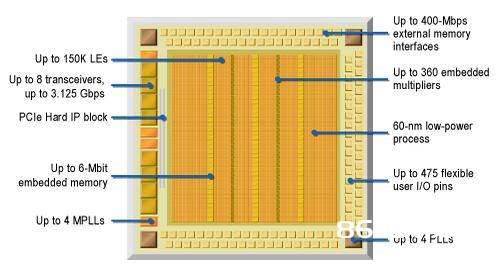

FPGA芯片的工艺结构-目前最大的两个FPGA厂商Altera公司和Xilinx公司的FPGA产品都是基于SRAM工艺来实现的。这种工艺的优点是可以用较低的成本来实现较高的密度和较高的性能;缺点是掉电后SRAM会失去所有配置,导致每次上电都需要重新加载。

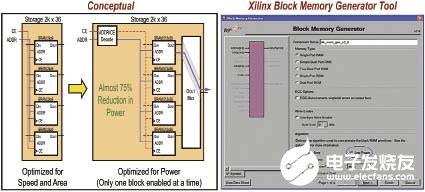

利用FPGA设计技术降低功耗,如何实现设计解决方案-在90nm工艺时,电流泄漏问题对ASIC和FPGA都变得相当严重。在65nm工艺下,这一问题更具挑战性。为获得更高的晶体管性能,必须降低阈值电压,但同时也加大了电流泄漏。Xilinx公司在降低电流泄漏方面做了许多努力,尽管如此,源于泄漏的静态功耗在最差和典型工艺条件下的变化仍然有2:1。泄漏功耗受内核电压(VCCINT)的影响很大,大约与其立方成比例,哪怕VCCINT仅上升5%,静态功耗就会提高约 15%。最后,泄漏电流还与结(或芯片)温密切相关。

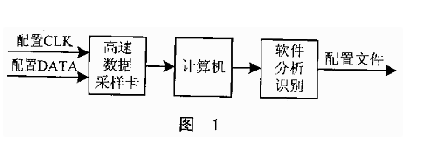

对SRAM工艺的FPGA进行加密的方法浅析-由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置的位数据流,进行克隆设计。因此,在关键、核心设备中,必须采用加密技术保护设计者的知识产权。

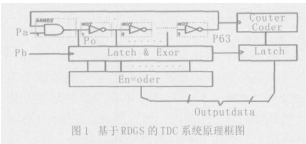

基于max7000芯片和可编程逻辑器件实现时间数字转换电路的设计-时间数字转换(tdc)技术原本是实验核物理中的课题,随着科学技术的不断发展,精密时间测量数字化技术在高能物理、雷达、激光和声纳测距、通信测向、遥感成像等都应用了高分辨率的tdc技术,全数字集成电路的工艺简单,造价较低,设计难度较小,是电路设计人员追求的目标,因此,全数字的tdc也成为研究人员关注的问题,文献报道了一种全数字化的模数变换电路(adc),该方法本质上是基于全数字tdc的,以0.8μm cmos工艺在0.45mm2面积上实现了18位全数字的adc,该芯片在10ks/s采样率下可以达到12μv分辨率,非线性度为±0.1%。文献报道了该系统的tdc原理和专用集成电路(asic),用1.5μm的cmas工艺以1.1mm2面积实现了13位的tdc,其分辨率仅为单个门的延时时间,约0.5ns。

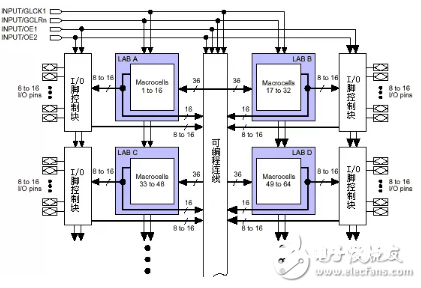

浅析PLD总体结构及逻辑实现原理-采用这种结构的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工艺),Xilinx的XC9500系列(Flash工艺)和Lattice,Cypress的大部分产品(EEPROM工艺)