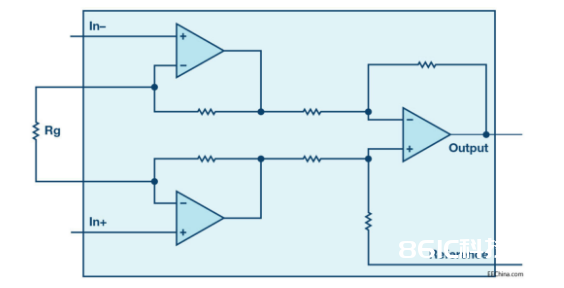

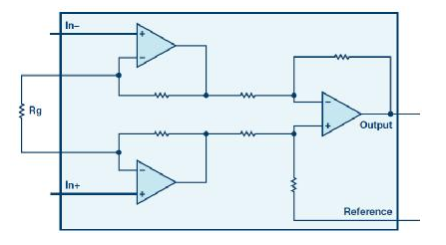

经典架构新玩法:用单端仪表放大器实现全差分输出-我们可以使用仪表放大器生成差分输出信号吗?随着对精度要求的不同提高,全差分信号链组件因出色的性能脱颖而出,这类组件的一个主要优点是可通过信号路由拾取噪声抑制。

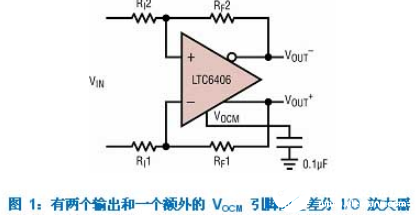

LTC6406等新的全差分运算放大器系列在单端应用中极其广泛-最近在低压硅锗和 BiCMOS 工艺技术领域的进步已经允许设计和生产速度非常高的放大器了。因为这些工艺技术是低压的,所以大多数放大器的设计都纳入了差分输入和输出,以恢复并最大限度地提高总的输出信号摆幅。因为很多低压应用是单端的,那么问题就出现了,“我怎样才能在一个单端应用中使用差分 I/O 放大器?”以及“这么使用可能产生什么结果?”本文探讨一些实际产生的结果,并展示一些具体和使用 3GHz 增益-带宽差分 I/O 放大器 LTC6406 的单端应用。

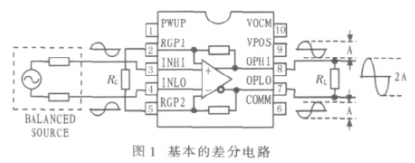

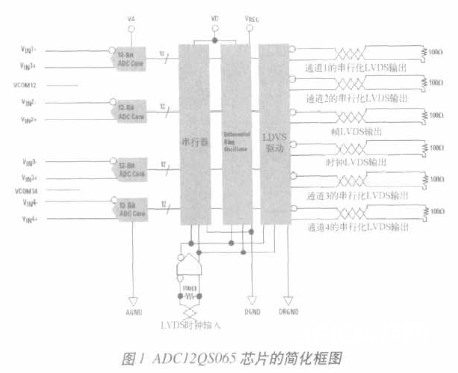

采用LVDS技术ADC12QS065芯片降低ADC布局的要求-当共模信号较难处理或对系统有负面影响的时候,需要进行信号调理。部分系统的设计会将模拟变换器输出的单端信号转为全差分信号,然后将这些信号传送到差分输入ADC。这种设计的优点是,大部分混入差分线路的噪声会同时出现在两条线路上 (假设差分线路都是按差分方式平衡布局)。

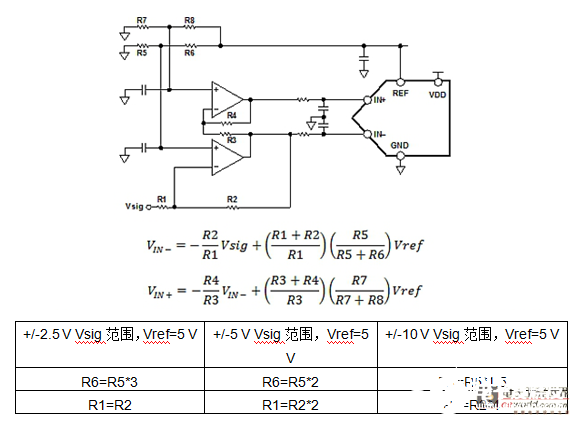

采用FDA方法如何有效的实现单端转差分-用这种方法实现的单端转差分具有最低的噪声,适合单电源类应用,可耐受阻性输入。 有关采用FDA的设计详情可参见应用笔记AN-1026:高速差分ADC驱动器设计考虑因素。 就噪声性能而言,似乎显然应该采用这种方法;然而,有些时候可能并不存在合适的FDA,而使用双放大器的定制电路可能更为合适。

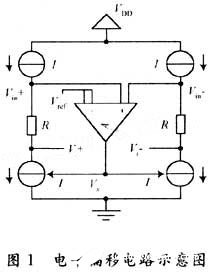

采用NMOS差分对结构实现低电压运算放大器的设计-已有文献[2]采用PMOS差分对来实现电源电压为1V的运算放大器,但由于Vt,PMOS的典型值为-0.75V,使得前置反馈电路的工作电平范围为1-0.15V,几乎涵盖整个共模电平范围,运算放大器的稳定性降低,另外,该结构下的折叠式共源共栅结构也会受体效应的影响,影响增益的恒定性。本文采用NMOS差分对结构,还对前置反馈电平偏移电路进行相应的改进,使电源电压降为0.9V的同时,提高了增益的恒定性。

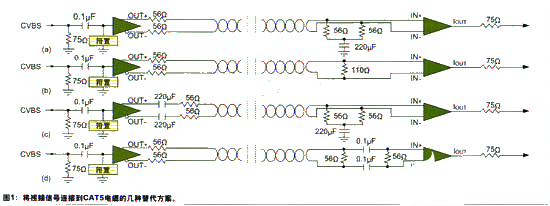

如何利用差分信令和CAT5网络电缆解决多通道视频的传输问题-采用CAT5电缆有几种基本的互连选择方案(67页图1),为应用选择最佳配置取决于具体条件以及为差分驱动器/接收器选择的IC。制造商通常会提供有关具体IC的最佳和效率最高配置的信息和实例,这里讨论的配置问题应提供附加指导,以帮助确定采用哪个选择方案可达到最佳效果。若我们有一个低压单电源(首选的)供电系统,一般需要在输入端增加视频箝位电路,以便在视频信号发生变化时维持正确的直流电平。在具有足够电压摆幅空间的双电源供电环境(±5V或同等电压)中不需要箝位电路。

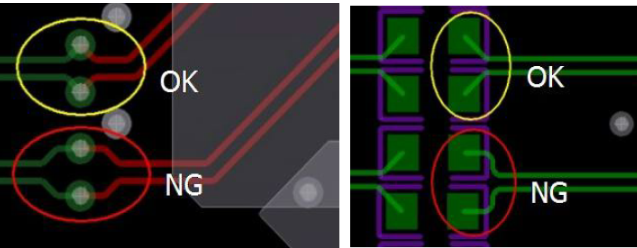

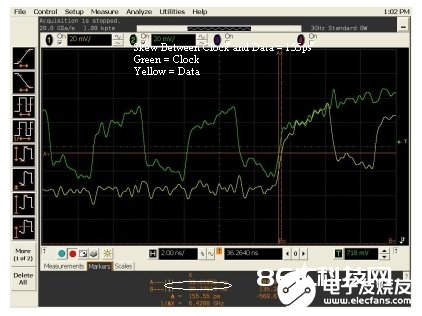

串行器/解码器的差分阻抗效应测量、调试和解决方法-当今许多手持电子设备都在LCD、照相机和键盘的接口电路中采用串行器/解码器(SerDes)技术。SerDes可以减少穿过铰链或滑动装置的信号数量,从而允许采用新的铰链或滑动装置,并可以降低成本。从并行传输线转换成串行传输线将产生差分阻抗的问题,差分阻抗将严重影响差分信号的完整性,导致LCD屏幕闪烁、射频干扰以及器件的容限问题。本文讨论手持电子设备中高速信号的差分阻抗效应,并讨论如何测量、调试和解决这些问题。