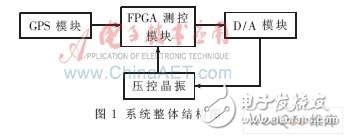

可同步于GPS的FPGA恒温晶振频率校准系统设计-设计中使用四路选通器分别连接计数器模块、延迟线模块和FIFO缓冲的输出,其中因计数器模块中采用16位的计数器循环计数,为了与PicoBlaze输入匹配,须将计数值分两部分接到选通器。异步串行控制器的输出和状态信息分别接到三路选通器,剩余一路连接四路选通器的输出。由于UART和PicoBlaze使用的时钟频率和测量部分不同,为了提高数据传输的可靠性,在选通器之间增加了流水线寄存器。

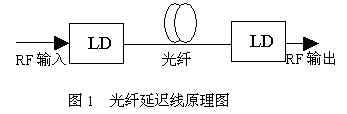

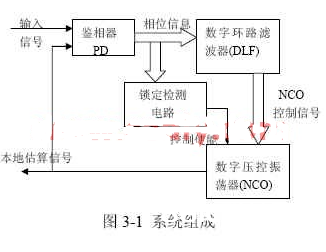

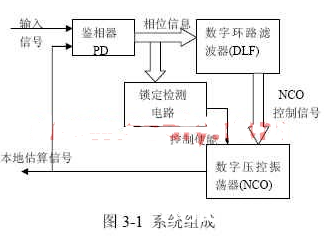

基于EPM7128SCL84-7芯片和quartus 2软件实现低频信号的锁相技术-在现代数字通信中, 数据传输,时钟校时等问题中很重要的一个方面是信号的同步。而同步系统中的核心技术就是锁相环。通常商用的全数字锁相环(DPLL)的关键部件是电荷泵和数字延迟线。电荷泵将数字鉴相器得到的相位差信息以电荷的方式累积起来,并根据积累的电荷量控制数字延迟线的反馈环,从而获得相应的本地估算时钟。即使是微小的相位差,也会导致电荷泵的电荷的累积。因此,这种技术实现的锁相环可以达到很高的同步精度。

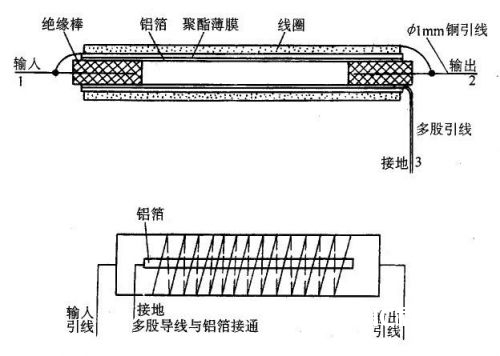

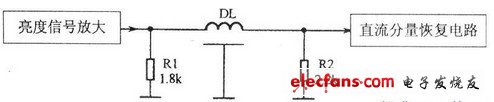

如下图所示是亮度延迟线应用电路。当亮度信号输入到这一延迟线后,其输出信号便经过了一定时间的延迟,约延迟0.6us。在此电路中,Rl是亮度延迟线输入端的阻抗匹配电阻,R2是亮度延迟线输出端的阻抗匹配电阻

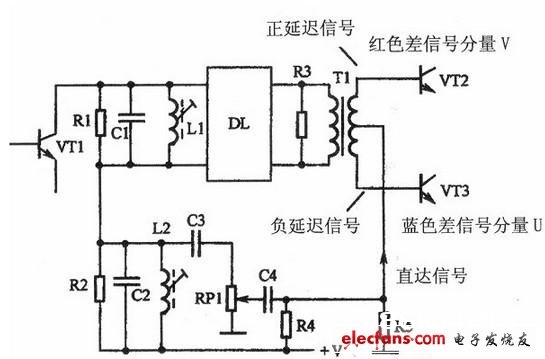

如下图所示是超声波色度延迟线电路,电路中的DL是超声波色度延迟线。VT1是色度信号F延迟放大管,VT2是红色差信号分量V信号放大管,VT3是蓝色差信号分量U信号放大管。从VT1集电极输出的信号分成两路

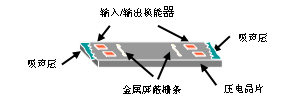

通过扇型结构换能器的优化设计和采用标准半导体平面工艺,研制出中心频率1.5~4.3GHz,工作带宽200~500MHz,时延0.05~3us的S、C波段声表面波微波延迟线。该系列产品的插入损耗为-22

基于EPM7128SCL84-7芯片和quartus 2软件实现低频信号的锁相技术-在现代数字通信中, 数据传输,时钟校时等问题中很重要的一个方面是信号的同步。而同步系统中的核心技术就是锁相环。通常商用的全数字锁相环(DPLL)的关键部件是电荷泵和数字延迟线。电荷泵将数字鉴相器得到的相位差信息以电荷的方式累积起来,并根据积累的电荷量控制数字延迟线的反馈环,从而获得相应的本地估算时钟。即使是微小的相位差,也会导致电荷泵的电荷的累积。因此,这种技术实现的锁相环可以达到很高的同步精度。