使用FPGA实现并/串转换电路-并串转换电路在通信接口中具有广泛的应用,可编程逻辑阵列由于具备灵活、可重构等特点非常适应于并串转换硬件电路的实现。为了解决硬件电路结构中资源与性能的矛盾,分析比较了移位寄存器、计数器与组合逻辑条件判定三种不同的并串转换硬件电路结构,并通过设计仿真对其进行了功能验证和性能评估。实验结果表明采用移位寄存器的实现方法具有最优的速度性能,采用计数器的实现方法具有最优的性价比。

设计FPGA系统的三个基本原则是什么,了解一下-在这种方法中面积的复制可以换取速度的提高。支持的速度越高,就意味着可以实现更高的产品性能。一些注重产品性能的应用领域可以采用并行处理技术,实现面积换速度。

基于Virtex-E系列XCV300E与高速静态存储设备的接口实现-为了能更好﹑更有效的设计FPGA与IS63LV1024的接口实现,必须先了解IS63LV1024的性能特点。充分利用这些特点会使设计的实现变得事半功倍。IS63LV1024是128K 8的高速静态存储器,性能特点包括:

使用嵌入式开发套件将软件编译并形成有效硬件-Xilinx Platform Studio(XPS)是一款普遍使用的嵌入式开发套件(EDK),其升级版XPS 8.2版本新增加了独特的功能和性能,可进一步提高嵌入式系统设计的效率,通过这一新版本,工程师可以获得针对目前业界速度非常快的FPGA产品,如Virtex-5 LX器件的嵌入式处理支持。下面将介绍XPS 8.2版本的一些新功能和增强的性能。

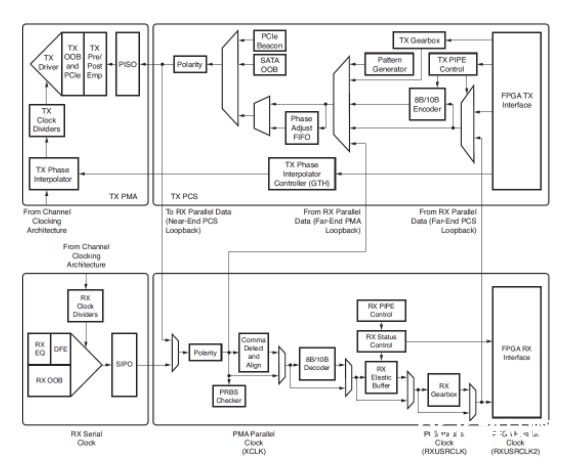

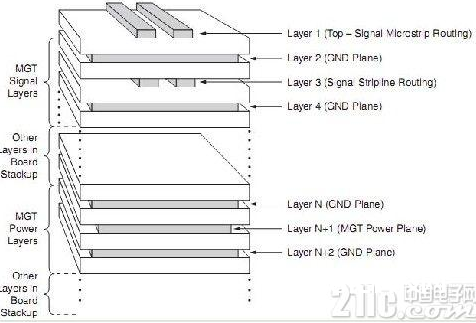

针对FPGA的GTP信号 PCB设计过程中需要考虑到以下因素-千兆位级串行I/O技术有着极其出色的优越性能,但这些优越的性能是需要条件来保证的,即优秀的信号完整性。例如,有个供应商报告说,他们第一次试图将高速、千兆位级串行设计用于某种特定应用时,失败率为90%。为了提高成功率,我们可能需要进行模拟仿真,并采用更复杂的新型旁路电路。

借助FPGA协同处理提升性能和降低应用设计成本-传统的、基于通用DSP处理器并运行由C语言开发的算法的高性能DSP平台,正在朝着使用FPGA预处理器和/或协处理器的方向发展。这一最新发展能够为产品提供巨大的性能、功耗和成本优势。

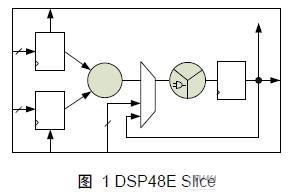

基于Adaboost算法结合Virtex5平台如何提升FPGA器件的性能-本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25×18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。

从FPGA到ACAP,赛灵思再次超越自我-赛灵思是FPGA的发明者。深鉴科技提供的一个实际案例表明,赛灵思在支持非常广泛的AI应用.作为可以和CPU、GPU与FPGA 相提并论、并且性能远超后二者的产品,ACAP可以覆盖更加广泛的应用.