采用VHDL语言在CPLD内部编程实现Flash读取控制设计-本设计已实用于国家863计划“可扩展到T比特的高性能IPv4/v6路由器基础平台及实验系统”项目中。其主要功能是对主控部分的FPGA读取Flash进行控制。

通过优化自动生成代码,帮助嵌入式系统开发人员将基于模型设计的方法扩展到ARM Cortex-A/R/M系列处理器上。中国北京 – 2014 年 11 月 5 日 – MathW

AT91SAM9263EKIAR内存容量从64M扩展到128Mbasic-lcd-project-at91sam9263-ek-iarbasic-lcd-project-at91sam9263-eka

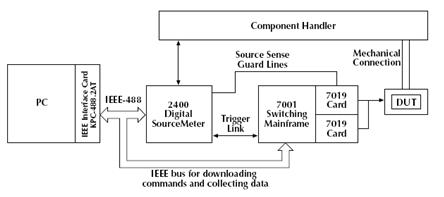

电子通信领域正迅速扩展到日常生活的各个方面。检测、传输和接收数据都需要使用大量器件,例如光纤传感器、RF MEMS、PIN二极管、APD、激光二极管、高压DAC等等。在许多情况下,这些器件需要几百伏的