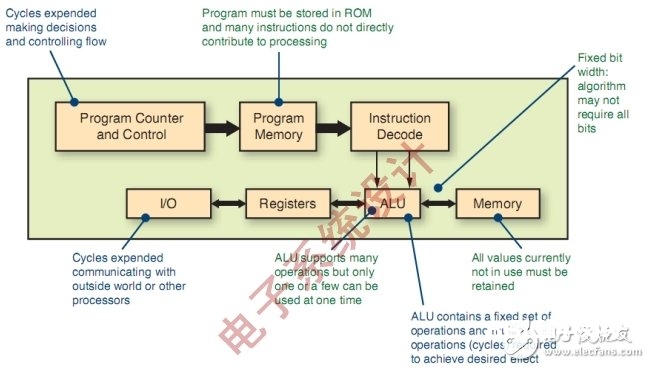

Xilinx滤波器IP核的延时问题-在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,但是阶数大小的选择要看是否满足自己的设计要求(例如衰减db是否满足要求)。同时,生成的滤波器抽头系数的值是与自己设计滤波器的各种参数确定的,如数据采样速率,通带截止频率、阻带起始频率(低通)、滤波器类型等。

如何利用FPGA技术来解决DSP的设计难题?-如果采用MAC模式,DSP48则非常适用,因为DSP48 Slice内含输入寄存器、输出寄存器和加法器单元。实现31抽头MAC引擎需要的资源包括一个DSP48、一个18kb块RAM(block RAM)和9个逻辑片。另外,还需要一些逻辑片用于采样、系数地址生成和控制。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx 7系列器件中,该滤波器能够以19.35MHz或1,935MS/s的输入采样速率运行。

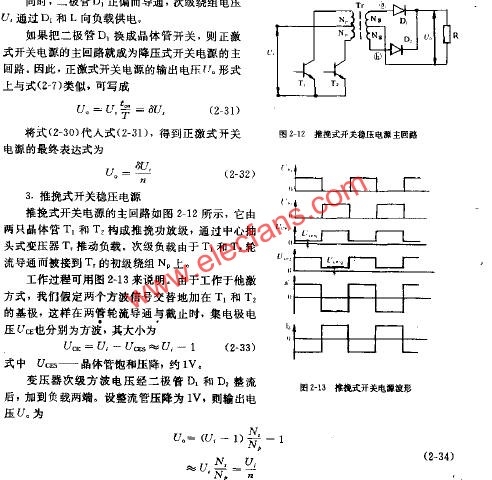

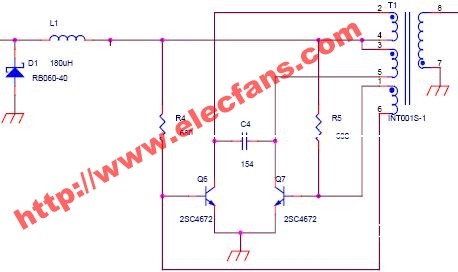

实际上是一个自激推挽式DCAC升压变换电路,由续流二极管,阻尼电感,两个PNP三极管,两个基极电阻,一个谐振电容及有3个绕组的变压器组成.L1为变压器的中心抽头提供一个高交流输入阻抗,R4R5为Q6Q

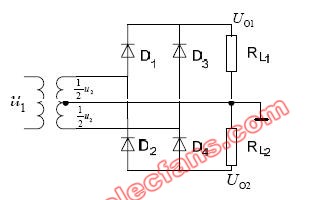

具有正负输出电压的桥式整流电路桥式整流电路除了可以得到全波输出外,如果变压器二次绕组具有中心抽头,只要把中心抽头接地,就可以很方便地获得正负输出电压,接线如图3.10a.4所示,其输出平均电压U01=

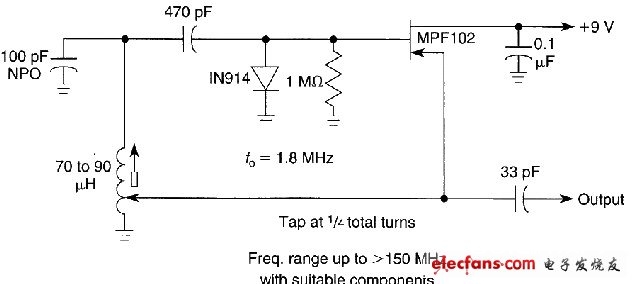

工作原理:本电路将传输的调频广播频段(88-108MHz)的可用于远程控制或安全用途的连续音频的音调。电路从一个吸引约306-9伏电池毫安,可接收到约100公尺。振荡器频率由5转抽头电感和13pF的电

LT108构成的负输出电压电路图中所示电路是在接地端进行电压控制,输入必须加浮置电源,否则不能耗工作,因此不能用于中间抽头的变压器同时构成正电源的电路,接低端阻抗高,寄生电容也大,容易载有高频噪声,这