基于级联结构和VHDL语言的IIR数字滤波器在FPGA上实现设计-IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同时钟速度下可以提供更好的带外衰减特性。下面介绍一种在FPGA上实现IIR数字滤波器的方法。

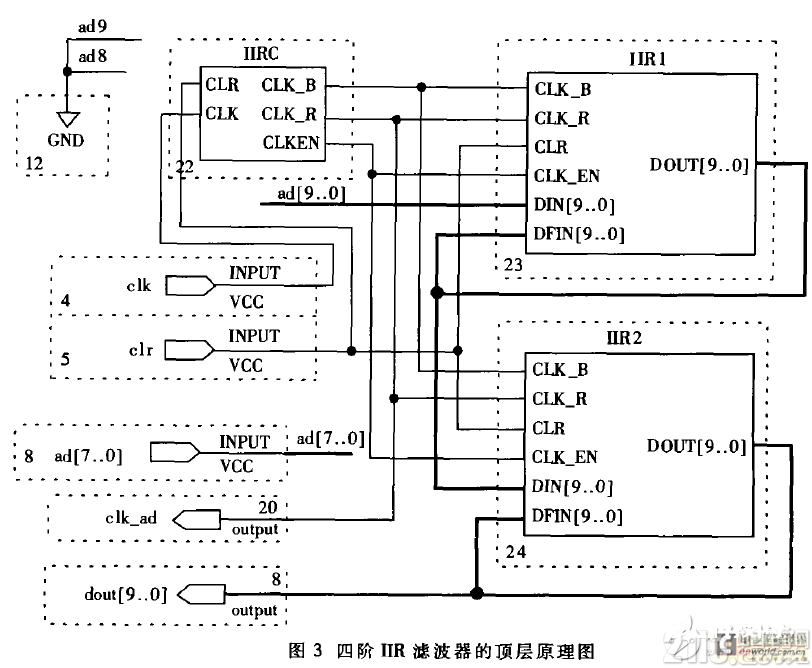

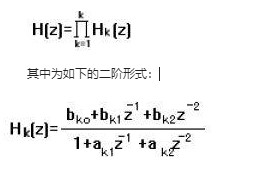

采用自顶向下的模块化设计思想,介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的设计方案。设计IIR数字滤波器的二阶节,将二阶节IIR数字滤波器级联实现高阶IIR数字滤波器,从而实现通过修改外围

提出了一种采用现场可编程门阵列器件FPGA并利用窗函数法实现线性FIR数字滤波器硬件电路的方案,并以一个十六阶低通FIR数字滤波器电路的实现为例说明了利用Xilinx公司XC4000系列芯片的设计过程