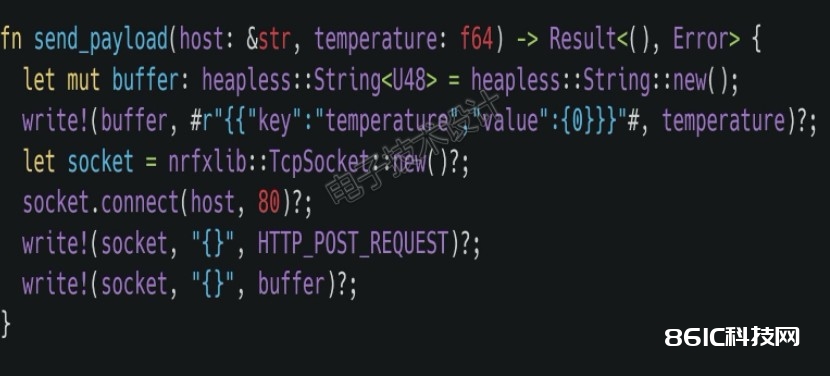

Rust编程语言推出独特“借阅检查器”功能-近年来,消费、医疗、农业、工业以及其他领域对物联网(IoT)连接的需求不断增长,产品开发咨询公司42 Technology表示,制造商希望为最终用户带来与众不同的产品,因此想利用物联网连接来添加功能,或为基于服务的产品生成新的数据流。

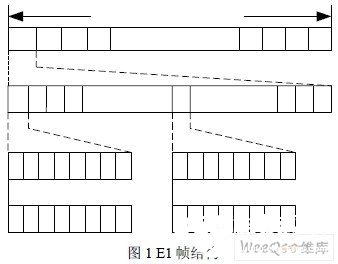

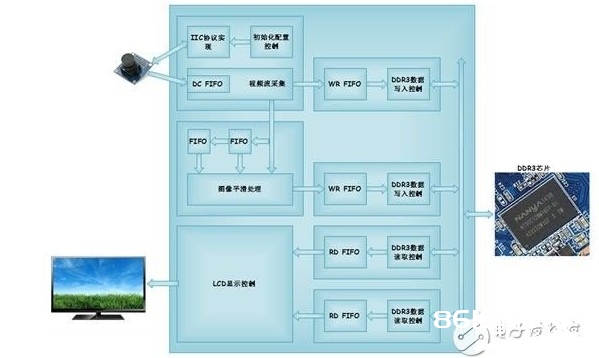

采用FPGA实现图像平滑处理-在FPGA内部,采集到的视频数据先通过一个FIFO,将原本25MHz频率下同步的数据流转换到50MHz的频率下。接着将这个数据再送入写DDR3缓存的异步FIFO中,这个FIFO中的数据一旦达到一定数量,就会写入DDR3中。

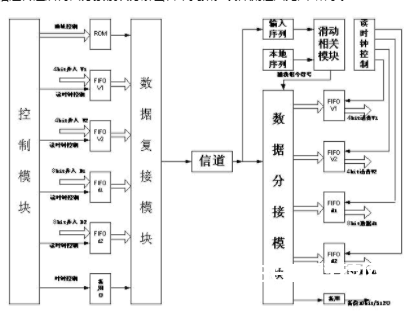

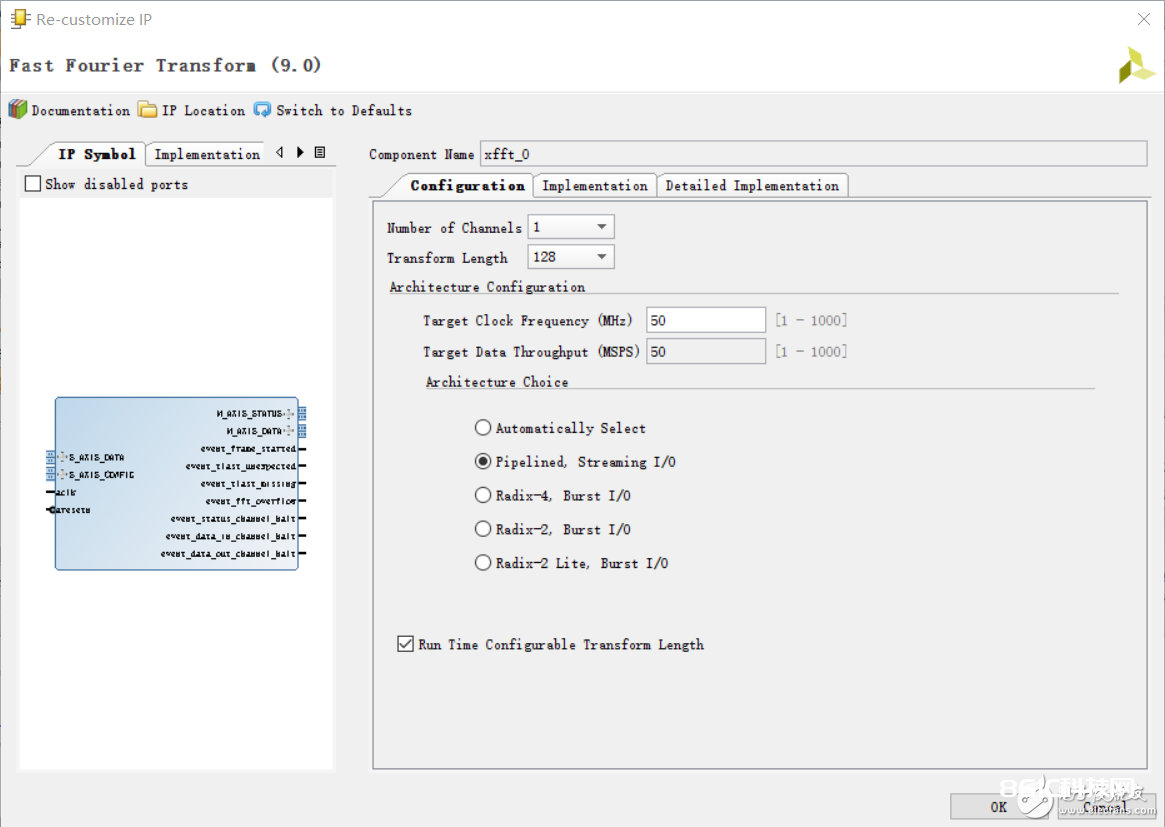

通过Xilinx FFT IP核的使用实现OFDM-由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。

HLS优化设计中pipeline以及unroll指令:细粒度并行优化的完美循环-HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定的代码风格。展开 (unroll) 指令是只针对 for 循环的展开指令,和流水线指令关系密切,所以我们放在一起首先我们来看一下这三个指令在 Xilinx 官方指南中的定义: Unroll: Unroll for-loops to create multiple instances of the loop body and its instructions that can then be scheduled independently. Pipel

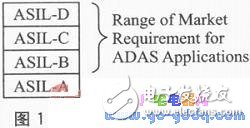

基于可编程FPGA在系统级实现诊断-本文以单前端摄像机系统为例,对其进行深入分析,介绍它如何通过使用ALTEra Cyclone V SoC确定关键数据流.在现有的诊断机制下,如何找到故障;并提供一些诊断实例,通过灵活的可编程FPGA,在系统级实现诊断。与使用通用微处理器、数字信号处理(DSP)和其他平台相比,在某些情况下,针对实际应用使用定制诊断方法可以提高应用性能。

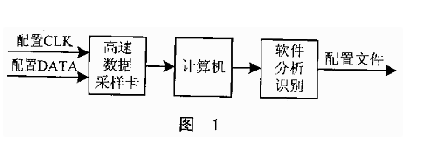

对SRAM工艺的FPGA进行加密的方法浅析-由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置的位数据流,进行克隆设计。因此,在关键、核心设备中,必须采用加密技术保护设计者的知识产权。