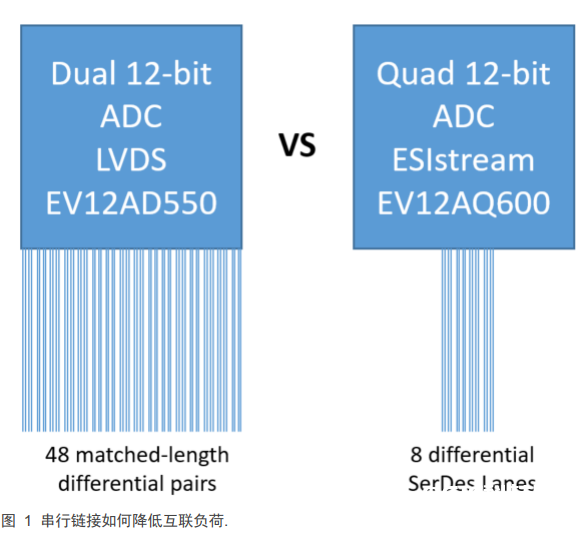

ESIstream IP–简化确定性数据序列化的设计-当使用现代宽带数据转换器时,管理产生的高速串行数据流是一个巨大的挑战。ESIstream 是一个开源的串行数据接口协议,成本极低,支持多种 FPGA 架构的简单硬件实现,并占用最小的资源。

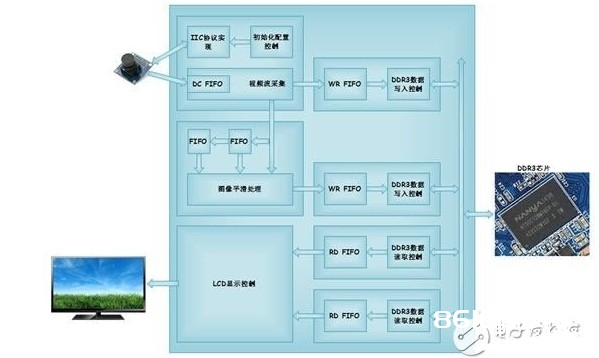

采用FPGA实现图像平滑处理-在FPGA内部,采集到的视频数据先通过一个FIFO,将原本25MHz频率下同步的数据流转换到50MHz的频率下。接着将这个数据再送入写DDR3缓存的异步FIFO中,这个FIFO中的数据一旦达到一定数量,就会写入DDR3中。

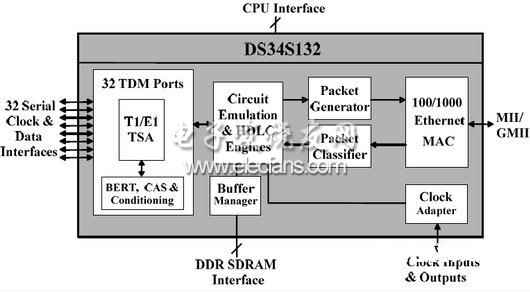

基于VIRTEX-ⅡPRO系列FPGA实现多业务双向通信系统的设计-随着现代通信向着多业务方向发展,为了节省信道资源、降低调制解调设备的复杂度,数据复接设备得到了更充分的利用。它能将多路不同类型的数据流复接成一路高速数据流,通过信道传输,在收端分接出发端对应的数据流,以实现多业务双向通信。

本站为您提供的DS34S132 32路独立TDM端口,IETF PWE3 SAToP/CESoPSN/HDLC兼容的DS34S132为L2TPv3/IP、UDP/IP、MPLS (MFA-8)以及城域以太网(MEF-8)网络提供将TDM数据流转换为TDM-over-Packet (TDMoP)数据流所需的全部交互功能,同时满足公共网络(ITU G.823、