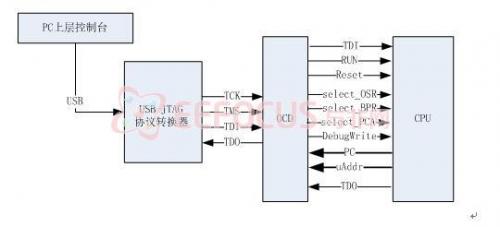

本文设计了一个基于JTAG协议的片上调试器,该片上调试器实现了微指令和机器指令的单步、断点以及读取处理器内部寄存器和写入PC、处理器复位等常用调试功能。构建扫描链时采用独立的扫描通路不对处理器本身寄存

以一款SPARC V8处理器为例,分析了处理器分级存储系统中Cache和MMU对断点调试实现的影响,提出有效的解决办法,并成功应用到该处理器的调试工具中。该方法也适用于其他具有Cache和MMU的处理

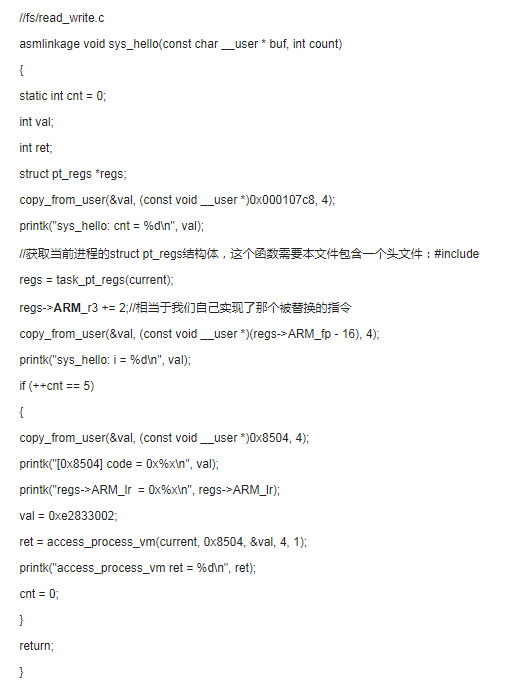

自写系统调用调试应用程序过程-比如我们想在C函数的i=i+2;处打断点的话,我们先在反汇编文件里面找到对应的指令:84d4: e2833002 add r3, r3, #2 ; 0x2 其中:e2833002是机器码,这是我们所需要的!

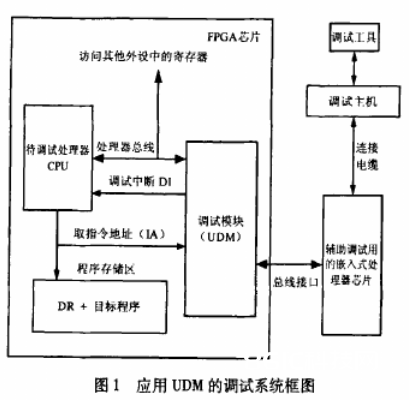

基于双端口RAM中多行代码设置断点功能实现新型通用调试模块的设计-在FPGA 设计中使用嵌入式处理器软核( 如MicroBlaze、PicoBlaze 等) 构成可编程片上系统( SystemOn Programmable Chip,SOPC) ,相比于ASIC 具有更好的可修改性和可维护性,得到了普遍的应用。由于ARM,MicroBlaze 等大型处理器内核具备调试接口,在与之对应的调试模块配合下,调试软件可以通过JTAG 接口实现: 执行到断点处挂起、单步执行、查看处理器内部状态、查看和修改Memory空间中的数据等基本的在线调试功能。上述基本的在线调试功能对嵌入式系统的调试具有重要意义。