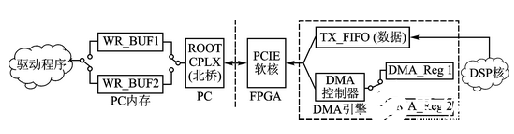

基于Xilinx Virtex6 FPGA的通用软件无线电平台设计-近年来软件无线电(SDR)得到了飞速的发展,在很多领域已显示出其优越性。本文的项目背景是通过软件无线电方式实现数字音频广播(DAB)的基带信号处理,这要求软件无线电平台具有高速实时数字信号处理与传输能力。高速可编程逻辑器件(FPGA)和丰富的IP核提供了能高效实现软件无线电技术的理想平台。

基于新型Virtex FPGA实现小型软件无线电平台SFF SDR设计-SFF SDR(小型软件定义无线电)开发平台是一种模块化的 RF/IF/基带平台(图 1 和图 2)。该平台展示了 Xilinx 和德州仪器 (Texas Instruments, TI) 的最新芯片产品以及最新高级设计流程和软件架构。 这个平台还为手持设备开发人员提供了特定的关键功能,如实时功耗配置和监测。

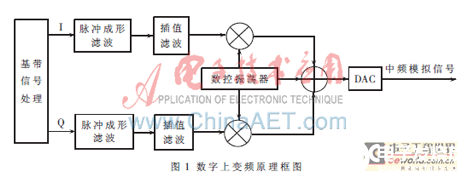

基于FPGA的高效灵活数字上变频实现设计-软件无线电的基本思想是把A/D变换器尽可能地靠近射频天线,用软件实现无线电系统的各种功能[1]。数字上变频器是软件无线电中发射机的核心部分,它的基本功能是增加基带信号采样率并将其上变频到载波频率上,经过发射天线发射出去。采用专用芯片实现数字上变频器集成度高,应用方便,但是缺少灵活性,在软件无线电中的应用受到限制,因此研究使用可编程的FPGA实现数字上变具有重要意义。

SoPC与CORDIC算法相结合的通用调制解调器设计方案-软件无线电要求在通用硬件平台上通过运行不同软件实现多种调制解调方式,这就要求为信号的调制及解调建立通用模型。当代无线通信中,理论上各种通信信号都可采用正交调制方法加以实现,所以,采用正交调制可以建立统一的模型,适用于软件无线电实现。

基于Vivado高层次综合工具评估IQ数据的无线电设备接口压缩算法设计- 我们使用 Vivado ®Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号保真度的影响、造成的时延及其实现成本。我们发现赛灵思的 Vivado HLS 平台能够高效评估和实现所选压缩算法。

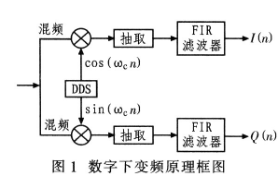

基于可编程逻辑器件实现数字下变频系统的设计-数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。基于这些优点,FPGA在软件无线电的研发中具有重要作用。

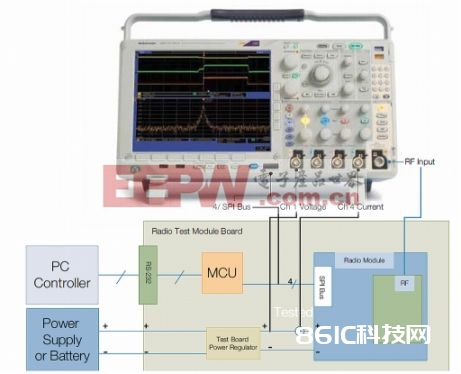

受全球变暖和能源价格上升的影响,市场对智能化、基于无线电控制的设备的需求快速增长,这些装置可用于监测、控制、传讯以及自动化能源和其他资源的输送。不过这只是基于物理层无线电标准的IEEE 802.15.