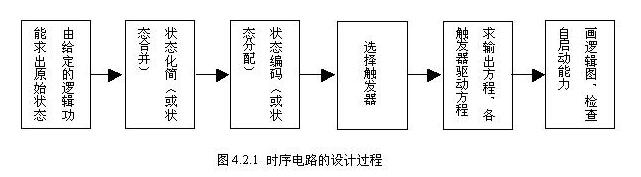

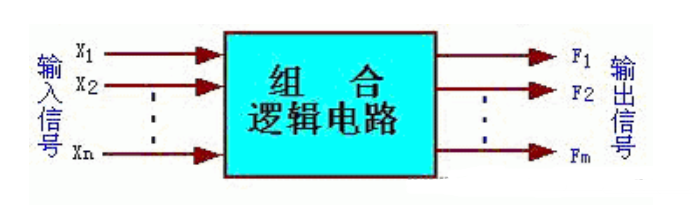

时序逻辑电路设计-数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

什么是组合逻辑电路 如何使用verilog描述组合逻辑电路-逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路。

linux内核调度与spinlock的相互关系-自旋锁在同一时刻只能被最多一个内核任务持有,所以一个时刻只有一个线程允许存在于临界区中。这点可以应用在多处理机器、或运行在单处理器上的抢占式内核中需要的锁定服务。

采用AVR单片机和GTJ4-10A固态继电器实现实时测量监控系统的设计-温度显示曲线图的主要任务是将单片机接收到的数据显示出来,当温度传过时,在软件中分别显示当前的温度值和时刻。通过MFC中的Time函数记录每一个温度值的时刻。并采用绘图函数将温度值和温度的当前时刻绘成曲线,然后再对数据特殊处理绘制成曲线图。在这里比较难处理的是实时的温度采集绘制曲线。

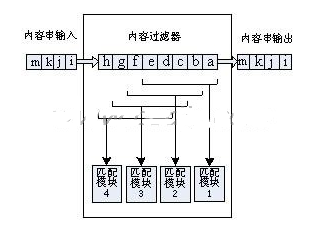

采用StratixII系列的EP2S60FPGA芯片实现报文内容过滤算法研究分析-可见,位置i上的hash函数可以通过i-1位置上的hash函数简单的算出。并且如果dij=di+1j的话,可见t时刻的hi和t+1时刻的hi-1是相同的,这样所有Hi就可以通过并行的移位结构在一个时钟周期内完成,而不用等待Hi-1的计算结果。相应的结构如图4所示,算法可以在一个时钟周期内算出所有Hi的值,非常便捷。

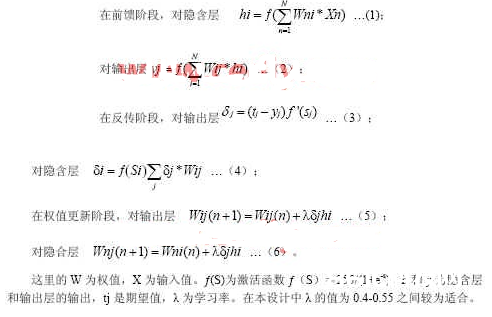

基于EP1C6Q240C8芯片的FPGA开发板实现神经网络恢复器的设计-本文使用了6输入1输出的BP神经网络结构,其隐含层选择了8个神经元。当传感器出现故障时,系统就根据传感器的所在位置和失效数据产生的时刻,将该时刻前一段时间的24组相应的输入输出数据对神经网络进行训练,调整神经网络的权值,逐步建立合理的BP神经网络模型。训练结束后,用该神经网络估算出该时刻传感器的真实值替代采样值,实现数据恢复。从前馈阶段开始,其算法的计算公式分别为: