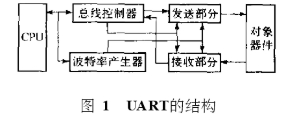

基于FPGA/CPLD器件和高级语言VB实现UART通信设计-随着计算机技术的发展和广泛应用,尤其是在工业控制领域的应用越来越广泛,计算机通信显的尤为重要。串行通信虽然使设备之间的连线大为减少,但随之带来串/并转换和位计数等问题,这使串行通信技术比并行通信技术更为复杂。串/并转换可用软件实现,也可用硬件实现。

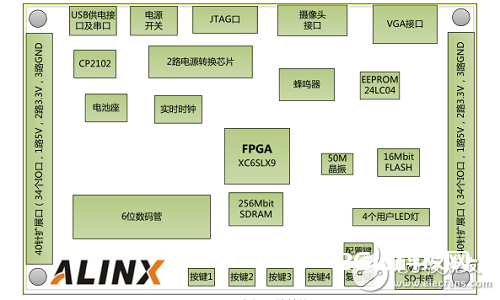

在嵌入FPGA的IP核8051微处理器上实现UIP协议栈的设计方法-在FPGA中植入8051后, 还可在上面实现简单的TCP/IP协议, 以支持远程访问或进行远程调试, 这只是在嵌入FPGA的8051上的一个应用。为了保证用户能够对8051实现不同的控制操作,设计时也可以采用一个外部flash对8051进行加载, 这样, 用户只需要将编译好的汇编语言代码加到flash就可以控制8051的工作, 而此时用户完全不需要对FPGA进行操作就能实现简单的控制,而这需要的仅仅只是keil的编译环境。

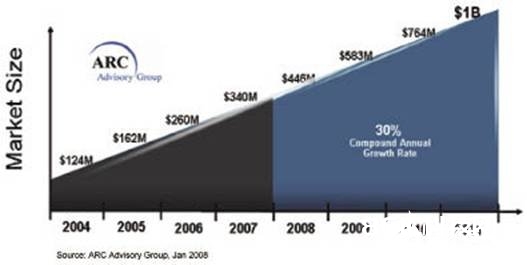

使用一个基于FPGA平台实现不同工业以太网协议的设计方法-对于速度和实时性能要求非常高的协议,在硬件中以专用协议MAC的形式实现实时功能。而协议的其他功能由运行在嵌入式处理器中的软件堆栈来完成,这些处理器可以是在 Cyclone III FPGA中实现的Nios II软核处理器。

基于FPGA +AD7609的数据采集系统的实现和设计-随着信息技术的发展,特别是各种数字处理器处理速度的提高,人们对数据采集系统的要求越来越高,特别是在一些需要在极短时间内完成大量数据采集的场合,对数据采集系统的速度提出了非常高的要求。

Stratix GX系列FPGA支持热插拔形式的设计-PLD热插拔的基本原理是在加电(VCCINT或任何VCCIO电源)或关电过程中关断输出缓冲。当VCCINT或VCCIO低于阈值电压时,热插拔电路都会产生一个内部的HOTSCKT信号,HOTSCKT信号将关断输出缓冲,以便确保没有直流电流通过管脚(不包括通过弱上拉电阻的漏电流)(见图1)。

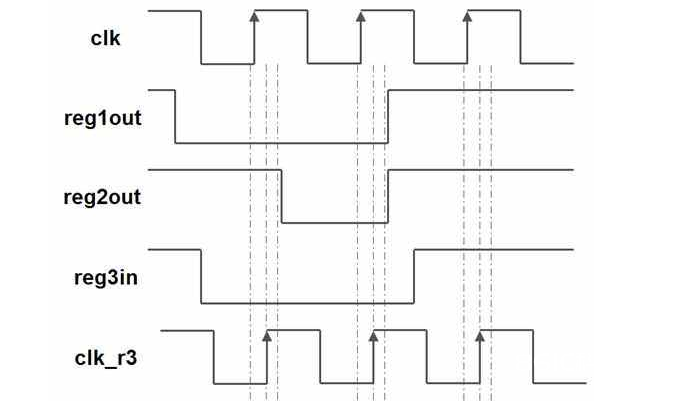

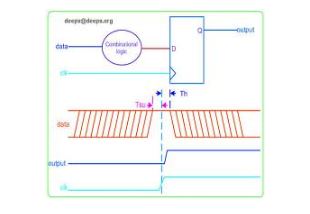

利用半拍错位同步法消除异步电路的亚稳态-当今的数字系统往往是围绕CPLD/ FPGA 进行设计的, 首选的方案是采用同步时序电路设计 , 也称作单时钟系统, 电路中所有触发器的时钟输入端共享同一个时钟, 每个触发器的状态变化都是在时钟的上升沿( 或下降沿) 完成的, 与时钟脉冲信号同步。

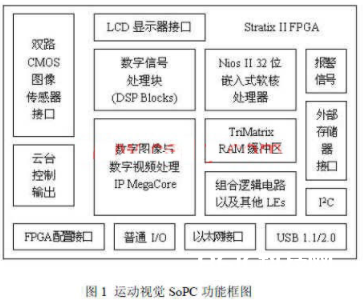

采用StratixII系列FPGA器件实现运动视觉处理系统的设计-该模块主要负责视频图像的采集,摄像头参数的设置和云台步进电机的控制。其中,通过 I2C总线可以设定摄像头内部控制寄存器。在 FPGA中,实现 I2C总线控制器的途径有两种:一种是在 Nios II中用软件模拟实现;另一种是采用第三方,比如 Sciworx,CAST,Digital Core Design等公司提供的 IP核。