STM8单片机增量的烧写方法-1 打开STVP

2 PROJECT/NEW,乱取个名来建立项目

3 PROJECT EDITION,首先在Configuration选好芯片,最重要的就是在SerialNumbering中来设置了

勾住Enable Serial Number,输入你要选中的地址,及字节数 起始值及步进值

4设置好了以后,选择“Properties”标签,配置编程动作。

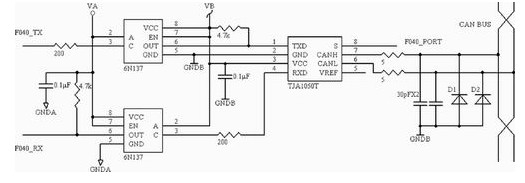

C8051F040单片机智能节点通信设计-C8051F040中的CAN寄存器分成3类: CAN控制器协议寄存器,消息对象接口寄存器,消息处理器寄存器。对于控制CAN主要功能的最重要的3个寄存器可以像单独的特殊功能寄存器( SFRs)一样采用直接访问的方式进行访问。它们分别是CAN控制寄存器,CAN测试寄存器和CAN状态寄存器。而对于其他一些寄存器则通过一个间接的指针机制进行访问。

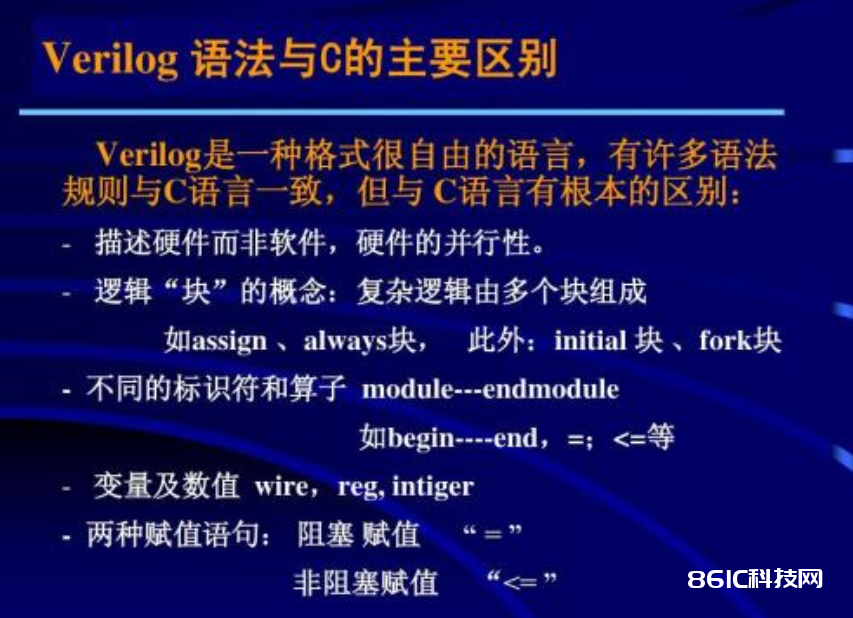

关于verilog的学习经验简单分享-学习verilog最重要的不是语法,“因为10%的语法就能完成90%的工作”,verilog语言常用语言就是always@(),if~else,case,assign这几个了。

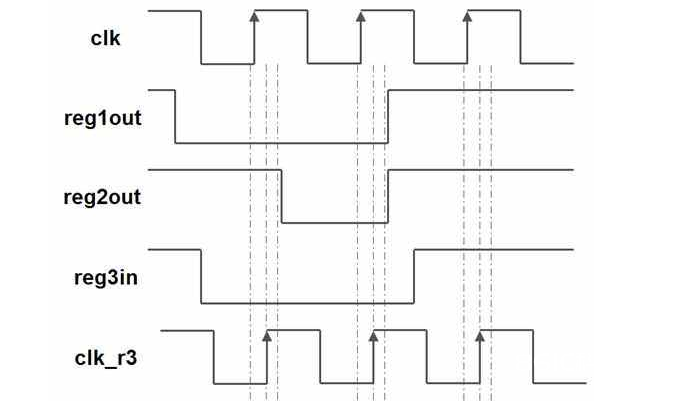

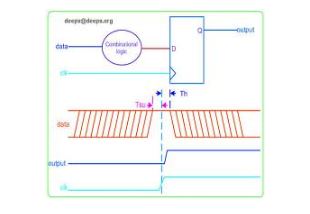

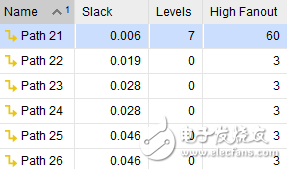

Vivado工程经验与各种时序约束技巧分享-首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡要在设计的早期阶段就要排除问题,越到后期时序的改善就越困难。其中HLS层次对性能的影响是最大的。

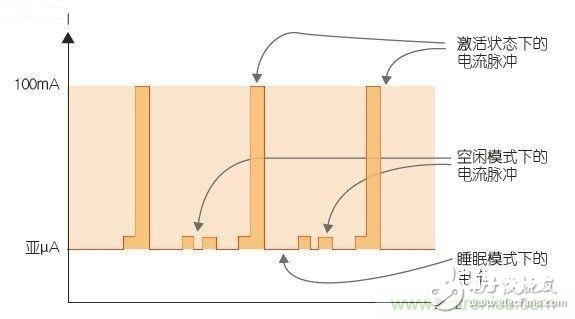

基于处理器实现USB 0TG控制器芯片的IP核应用设计-OTGl.Oa补充规范对USB2.O进行的最重要扩展是其更具节能性、电源管理,并允许设备以主机和外设2种形式工作。OTG有两种设备类型:两用 OTG设备(dual—role 0TG device)和外设式OTG设备(peripher一al_only 0TG device)。两用0TG设备完全符合USB2.O规范,同时提供有限的主机能力和一个Mini—AB插座,支持主机流通协议(IIost Negotiation Protocol,HNP)”。