Xilinx新一代UltraScale架构成为ASIC或SOC原型验证的极佳选择-近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

虽然交错式ADC具有极佳的速度和带宽性能等优势,而除此之外交错式ADC仍存在一些问题和不足之处。这些问题主要围绕ADC的噪声源展开。评估ADC噪声的具体情形时,噪声进入ADC的方式是最具参考价值的。因

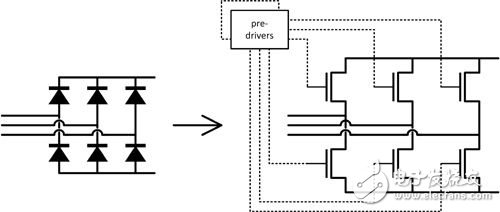

深谈汽车动力系统电路设计中的传感技术-本文将首先审视一些跟伦德尔(Lundell)式电动机(更广为人知的名称是“交流发电机”)相关的持续改进的极佳示例。由于采用了更好的电子控制,它的能效提升了,更多的

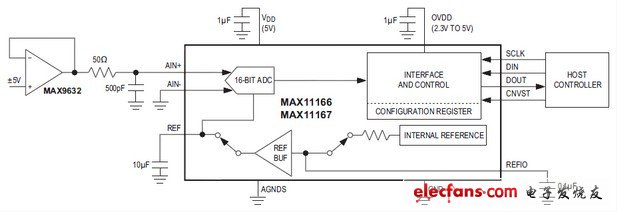

本站为您提供的MAX11166业内尺寸最小的16位ADC,支持±5V双极性性输入,MAX11166/MAX11167 16位,500ksps/250ksps,SAR ADC提供了极佳的AC和DC性能,具有真双极性输入范围,体积小,内部参考。