FPGA/CPLD数字电路原理解析-当产生门控时钟的组合逻辑超过一级时,证设计项目的可靠性变得很困难。即使样机或仿真结果没有显示出静态险象,但实际上仍然可能存在着危险。通常,我们不应该用多级组合逻辑去

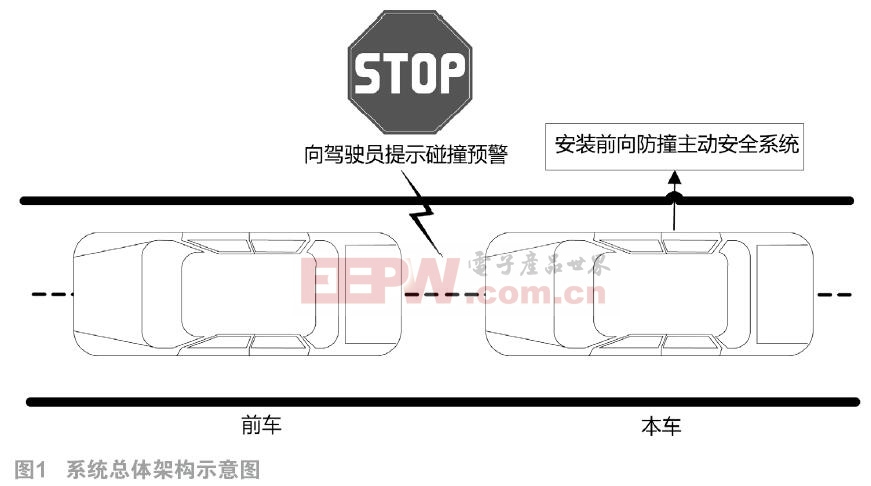

以摄像头采集的视频图像为输入,以ADSP-BF609微处理器为运算处理核心,详细描述了汽车前向防撞主动安全辅助系统的硬件平台架构和各个模块电路设计,并研制了样机。实验表明,电路设计可靠稳定,为汽车高级

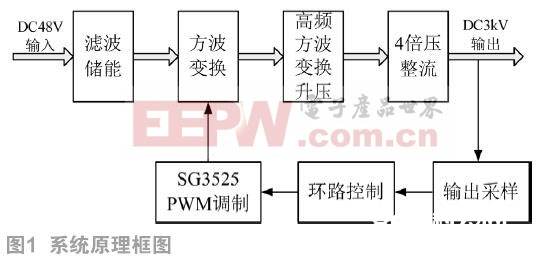

做了这么些年的开关电源设计,一个很让我心里忐忑的事就是新做的样机进行初次上电,担心炸机。相信很多工程师跟我一样深有体会,把自己的新样机在上电之前检查再检查,生怕哪个地方有焊错焊反搭焊或者说有地方短路,