PIC单片机的复位系统模块与中断模块介绍-每次单片机加电时,上电复位电路都要对电源电压VDD的上升过程进行检测,当VDD值上升到规定值1.6~1.8V时,就产生一个有效的复位信号,需经过72ms加1024个时钟周期的延时,才会使单片机复位。

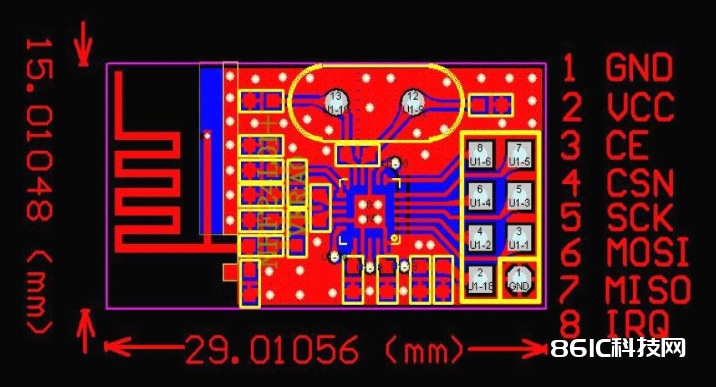

nRF24L01无线模块在PIC16F877单片机上的应用解析-通过SPI方式完成数据的交换,包括数据的发送,数据的接收。说明一下,单片机中如果没有SPI的硬件电路,我们可以使用单片机的普通IO口进行SPI的时序模拟,只要符合无线模块的时序逻辑,一样能控制无线模块的通信。

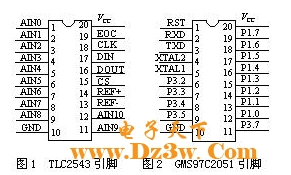

基于GMS97C2051单片机的串行数据采集模块设计-模块采用TI公司的TLC2543 12位串行A/D转换器,使用开关电容逐次逼近技术完成A/D转换过程。由于是串行输入结构,能够节省51系列单片机I/O资源,且价格适中。

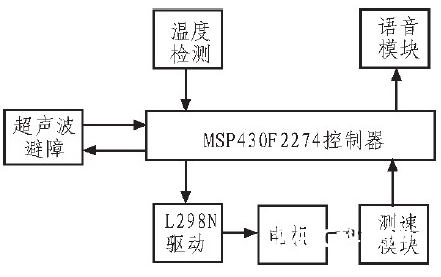

MSP430单片机对智能小车的硬件控制设计-该系统主要由MSP430控制器,超声波避障模块,电机驱动,测速,语音模块,温度模块,小车的机械运动部分采用四轮差速转向式结构,前2个轮是驱动轮,分别由电机控制其运动,后两轮为随动轮。

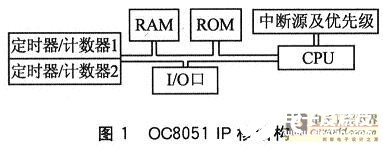

基于OC8051IP核的仿真调试方案在FPGA中实现下载测试-OpenCores网站提供的OC8051 IP核与8051的系统结构相同,如图1所示。该IP核兼容所有8051指令系统,内部资源包括:8位CPU,寻址能力达2×64K;4 KB的ROM和128字节的RAM;4个8位I/O口;16位内部定时/计数器;5个中断源和2个中断优先级。采用Verilog语言对其各个模块进行描述。系统主要模块及其功能说明如表1所列。不同模块对应的源文件均是以模块名称命名的,例如累加器A对应的源文件为oc8051_acc.v。

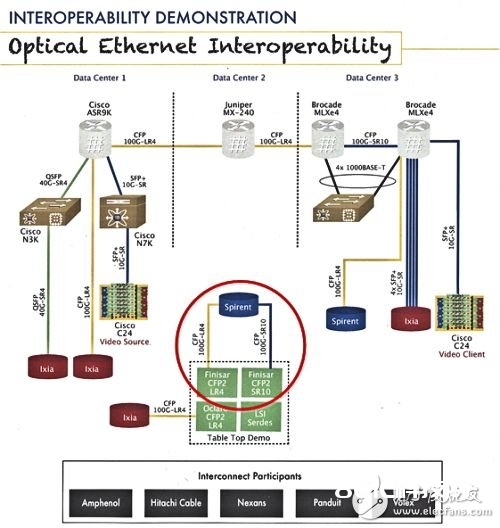

光学以太网互操作性介绍-Steve Leibson , Xilinx 战略市场营销和商业规划总监 我刚刚参加完在阿纳海姆举行的 OFC/NFOEC 会议,期间每天的所有议题都是高速光纤通信。在展会上,我在三个不同的展台观摩了三场不同的 100G CFP2 光模块演示: Oclaro 展台演示的是 Oclaro LR4 CFP2 模块;以太网联盟( Ethernet Alliance )展台演示的是 Finisar 100GBASe-LR4 CFP2 模块;而光互联网络论坛( OIF )展台则展示了富士通光器件有限公司( Fujitsu Optical Components )的 100GbE CFP LR4 收发器。

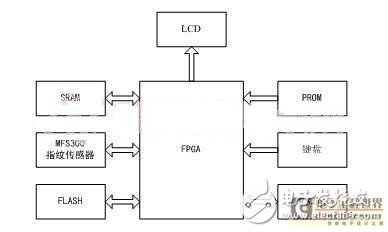

基于FPGA的指纹识别模块设计方案-本模块采用xilinx公司的 Spartan 3E 系列XC3S500E型FPGA作为核心控制芯片,通过富士通公司的MFS300滑动式电容指纹传感器对指纹图象进行提取,然后对提取的指纹图像进行灰度滤波、图像增强、二值化、二值去噪、细化等预处理,得到清晰的指纹图象,再从清晰的指纹图象中提取指纹特征点,存入外部FLASH作为建档模板。

关于FPGA的FMC接口的详细介绍-FMC ( FPGA Mezzanine Card ) FPGA中间层板卡,整个FMC模块由子板模块、载卡两部分构成。子板模块和载卡之间由连接器连接,子板模块上连接器使用公座(male),载卡上连接器使用母座(female)。