关于PLC的五大功能你知道多少-PLC可用于对直线运动或圆周运动的控制。早期直接用开关量I/O模块连接位置传感器和执行机构,现在一般是拥有专用的运动控制模块,世界上各主要PLC厂家生产的PLC几乎都有运动控制功能。

基于EP1K10TC100-3 FPGA和微控制器实现数据采集系统的应用方案-基于 FPGA 的数据采集系统的总体功能模块如下图1 所示。系统有由FPGA、串行被动 配置模块、USB 通信模块、电源模块、显示模块、模数转换模块、数模转换模块等几个模 块组成。

基于XC3S400PQ208 FPGA芯片实现异步FIFO模块的设计-随着数字电子系统设计规模的扩大,一些实际应用系统中往往含有多个时钟,数据不可避免地要在不同的时钟域之间传递。如何在异步时钟之间传输数据,是数据传输中一个至关重要的问题,而采用FIFO正是解决这一问题的有效方法。异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部 FIFO 芯片更能提高系统的稳定性。

基于LabVIEW FPGA模块程序设计特点的FIFO深度设定详解-为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO不同深度的实验表明,采用该方法设定的FIFO深度能够比较好地满足系统对数据连续传输的要求。研究结果对深入展开研究和工程设计具有一定的指导意义。

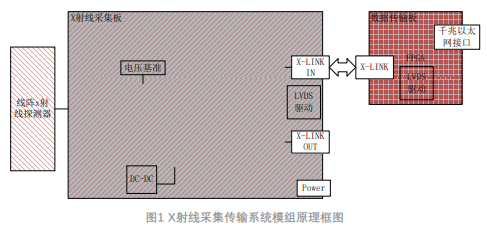

基于Cyclone IV系列FPGA实现X射线采集传输系统的设计-本文设计的X射线采集传输系统的硬件框图如图1所示。图像采集与传输系统的硬件包含三个部分,X射线探测器模块、FPGA数据采集模块和千兆以太网RGMII数据传输模块。

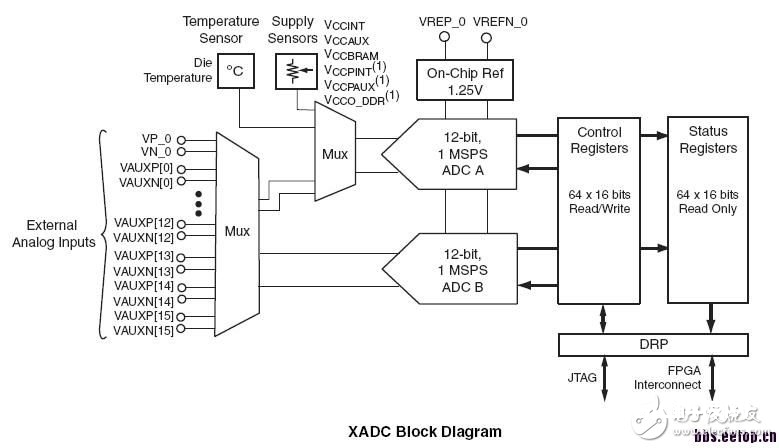

关于XADC模块的介绍和基本使用方法-Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图。

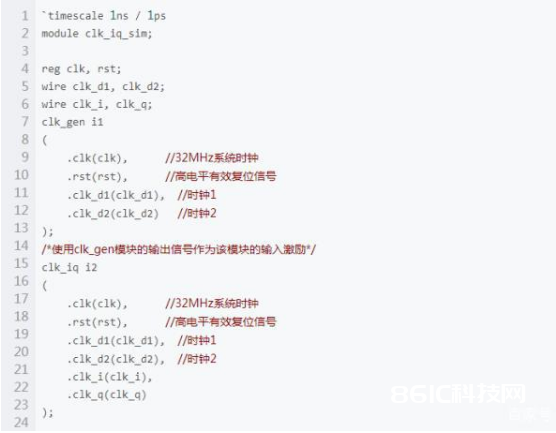

关于testbench在FPGA编程中的技巧-定义信号类型:原来模块中的输入信号,定义成reg 类型,原来模块中的输出信号,定义为wire类型,但这里有个问题,如果在testbench中本身有一个模块需要,如用来产生时钟,送给要仿真的模块,那怎么定义信号类型呢?

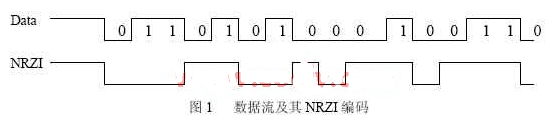

使用CPLD器件和VHDL语言实现USB收发模块的硬件功能设计-当前,高密度可编程逻辑器件CPLD,由于具有巨大的灵活性而广泛应用于状态机、同步、译码、解码、计数、总线接口、串并转换等很多方面,而且在信号处理领域的应用也活跃起来。通用串行总线(USB,Universal Serial Bus)接口既是一种快速、双向、廉价、可以进行热插拔的串行接口技术,也是一种体系完备的通信协议,已逐渐成为计算机的主流接口。USB接口的收发模块用于进行数据编码和与外部相连。本文主要介绍使用CPLD实现通用串行总线(USB)接口收发模块。

FPGA的工作原理以及内部结构-FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。