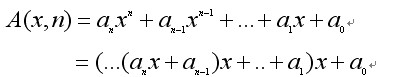

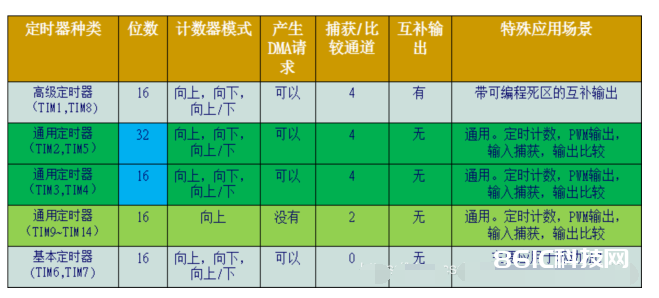

STM32定时器原理与使用-定时器的定时时间等于计数器的中断周期乘以中断的次数。计数器在 CK_CNT 的驱动下,计一个数的时间则是 CK_CLK 的倒数,等于:1/(TIMxCLK/(PSC+1)),产生一次中断的时间则等于:1/(CK_CLK * ARR)。如果在中断服务程序里面设置一个变量 time,用来记录中断的次数,那么就可以计算出我们需要的定时时间等于: 1/CK_CLK *(ARR+1)*time。

Verilog可综合的循环语句-Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

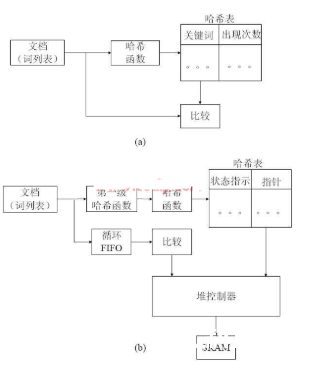

基于Xilinx Virtex-II FPGA的硬件哈希算法的研究分析-在计算关键词在文档里出现次数的过程中,需要一种存储结构来存储相关信息,这种存储结构必须易于执行查找、插入及删除操作。哈希是一种以常数平均时间执行查找、插入和删除操作的算法。在计算关键词在文档里的出现次数时应用哈希算法可以大大降低查找次数 。理想的哈希表数据结构是一个包含有关键字的具有固定大小的数组。