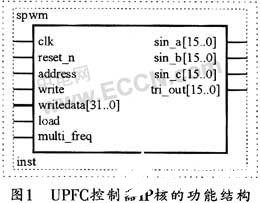

使用Altera CycloneIIEP2C35评估板实现UPFC控制器IP核的设计-UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波形数据和3路相位分别相差2π/3的三角载波波形数据。由于UPFC控制系统采用SPWM调制技术,所以要求UPFC控制器IP输出的正弦波频率应跟电网频率保持一致,输出的正弦波幅值和相位可以根据需要进行调节;而输出的三角载波频率、幅值和相位则保持不变。

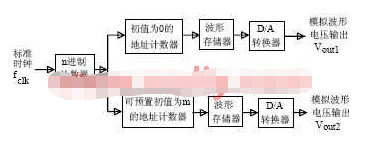

基于FPGA器件和VHDL语言实现波形及移相波形发生器的系统设计-标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

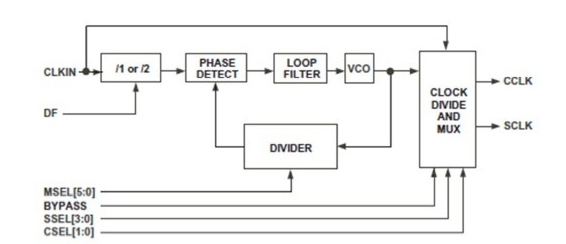

基于ADSP-BF531处理器的时钟及锁相环-ADSP-BF531处理器使用来自外部晶体的正弦输入,或经过缓冲整形的外部时钟。如果使用外部时钟,该时钟信号应是TTL兼容信号,而且正常运行时,此时钟不能停止、改变、或低于指定的频率。

三相SPWM的产生一般可以通过三相相位上互差120deg;的正弦波与三角波比较来实现。三相正弦表可以由三个独立的相位互差120deg;的正弦表组成,这在设计思路上是简单的,但实际中却有很大的浪费。 目

单相参考正弦波发生器电路图图单相参考正弦波发生器由于正弦波的对称性,仅算出T/4(T为调制波周期)的权电阻即可。mf=30的一种电路如图2所示。u0为半波正弦,由此可得到两路反相的双极性的正弦调制波。

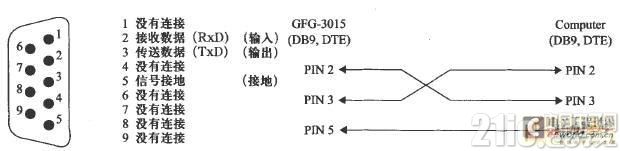

RS232总线的控制系统开发,引言 在飞机飞控系统地面模拟试验中,常常需要函数信号发生器、动态分析仪等传统仪器给被测系统注入正弦、阶跃和扫频等信号。这些仪器往往存在着操作比较繁琐,容易误操作引起系统损