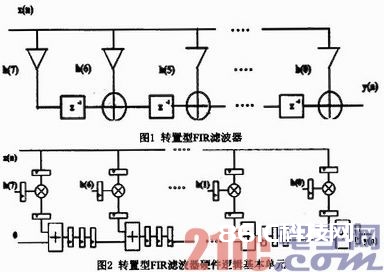

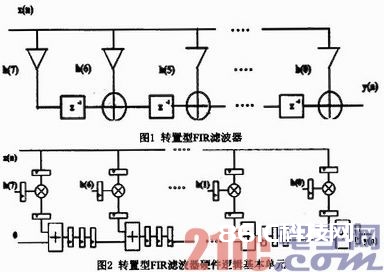

摘要:有限冲击响应(FIR)滤波器是数字通信系统中常用的基本模块。文章设计了一种流水结构的FIR滤波器,通过FPGA对其进行硬什加速控制。仿真结果验证了所设计的FIR流水结构滤波器功能的正确性。0 引

SoC是大规模集成电路的发展趋势。SoC设计必须依靠完整的系统级验证来保证其正确性。基于FPGA的验证平台能够缩短SoC验证时间,并提高验证工作的可靠性,还具有可重用性。本文利用Altera公司的FP

摘要:有限冲击响应(FIR)滤波器是数字通信系统中常用的基本模块。文章设计了一种流水结构的FIR滤波器,通过FPGA对其进行硬什加速控制。仿真结果验证了所设计的FIR流水结构滤波器功能的正确性。0 引

SoC是大规模集成电路的发展趋势。SoC设计必须依靠完整的系统级验证来保证其正确性。基于FPGA的验证平台能够缩短SoC验证时间,并提高验证工作的可靠性,还具有可重用性。本文利用Altera公司的FP