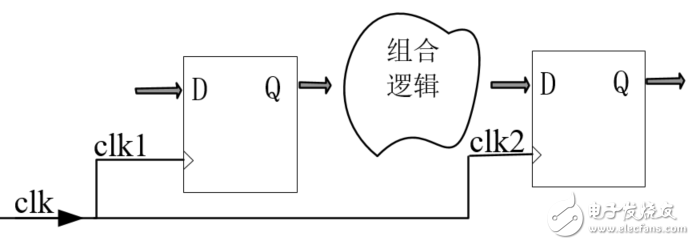

MCU时钟设计方案-两个时钟频率可以彼此完全无关,或者它们可以是彼此的倍数。在任何一种情况下,都有可能在切换时在时钟线上产生毛刺。时钟线上的毛刺对整个系统是危险的,因为它可能被某些寄存器解释为捕获时钟边沿而被其他寄存器忽略。

状态机和组合逻辑的冒险竞争浅析-有限状态机(Finite State Machine, FSM),根据状态机的输出是否与输入有关,可分为Moore型状态机和Mealy型状态机。Moore型状态机输出仅仅与现态有关和Mealy型状态机不仅与现态有关,也与输入有关,所以会受到输入的干扰,可能会产生毛刺(Glith)的现象,所以我们通常使用的是Moore型状态机。

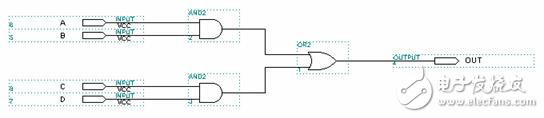

FPGA中的冒险现象和如何处理毛刺-通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

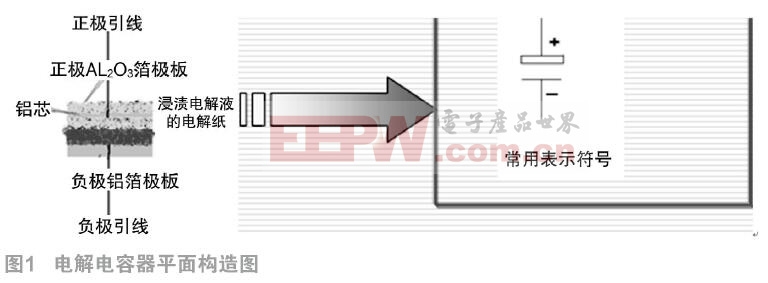

电解电容短路问题一直是行业内的整改顽疾,因其本身的结构及制造工艺限制,短路问题经常存在不稳定性,在实际生产应用过程中常因该问题导致批量的封存返包,而根据分析情况,电容内部的铝箔首卷位置毛刺短路(铝箔裁

该篇将分析对象限定为一个DAC,其中的输出缓冲器在正常模式下被加电:零量程或中量程。文章将分析一下DAC输出在高阻抗模式中被加电的情况。同时提出一个针对加电毛刺脉冲的数学模型,随后给出一个尽可能减少此

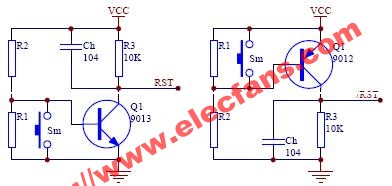

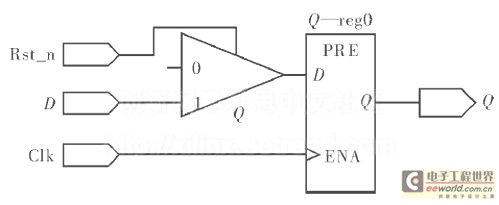

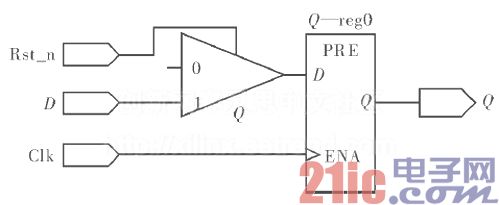

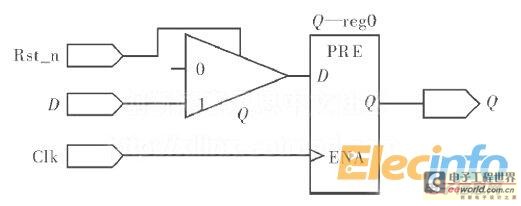

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步

电源电路设计中,对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,本文例举了提高复位设计可靠性的几种方法,也就是采用清除复位信号上的毛刺、异步复位