自动影像测量仪是在数字化影像测量仪的基础加上了基于机器视觉的自动边缘提取、自动理匹去毛刺、自动测量合成,从而具有了点哪走哪、自动测量;CNC走位、自动测量;自动学习、批量测量等十分优异的功能。同时,基

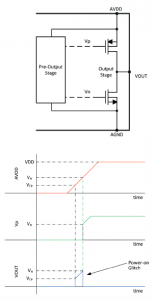

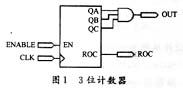

只要输入信号同时变化,(经过内部走线)组合逻辑必将产生毛刺。将它们的输出直接连接到时钟输入端、清零或置位端口的设计方法是错误的,这可能会导致严重的后果。 所以我们必须检查设计中所有时钟、清零和置位等对

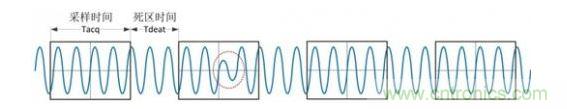

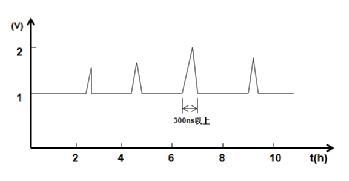

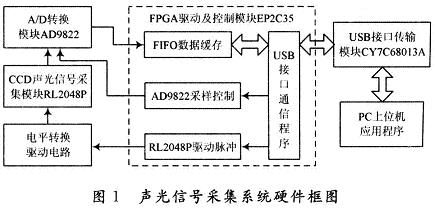

毛刺问题在FPGA设计中非常关键,只有深刻理解毛刺的本质,才有可能真正掌握设计的精髓,本文就FPGA设计中的毛刺问题进行了深入的探讨,分析其产生的原因和条件,给出了几种常用的消除方法,希望对FPGA设