如何利用FPGA技术来解决DSP的设计难题?-如果采用MAC模式,DSP48则非常适用,因为DSP48 Slice内含输入寄存器、输出寄存器和加法器单元。实现31抽头MAC引擎需要的资源包括一个DSP48、一个18kb块RAM(block RAM)和9个逻辑片。另外,还需要一些逻辑片用于采样、系数地址生成和控制。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx 7系列器件中,该滤波器能够以19.35MHz或1,935MS/s的输入采样速率运行。

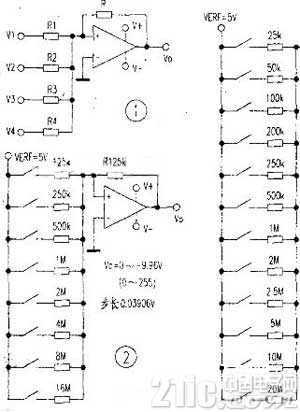

方波转换成正弦波电路即利用RDD104可选的4各十进制CMOS除法器和一个MSFS5开关电容滤波器来构建一个双芯片、失真率为0.2%的正弦波源。RDD104有两个引脚,可以从四个除法器divide-b

简要地介绍了M序列码作为同步头的帧同步提取的原理。在研究了相关处理的基础上,提出了采用补码配对相减匹配滤波法实现同步提取的新方法。该方法仅利用减法器和加法器,不仅使电路设计简单,而且使电路得到极大的优

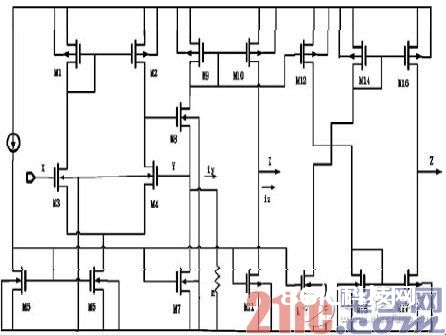

本设计充分利用了Vertex器件的LUTs(Look-Up Tables)替代触发器和基本门电路搭建乘法器和加法器这两个显著的结构特点,节省了大量的触发器资源,增加了器件利用率、布通率,DLL的运用降