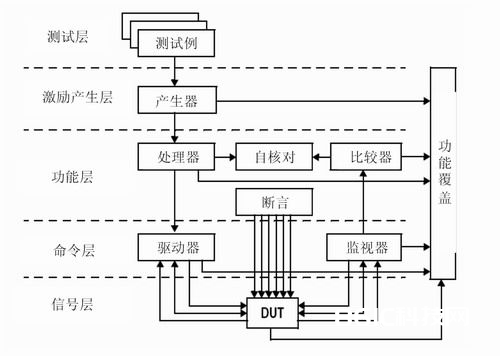

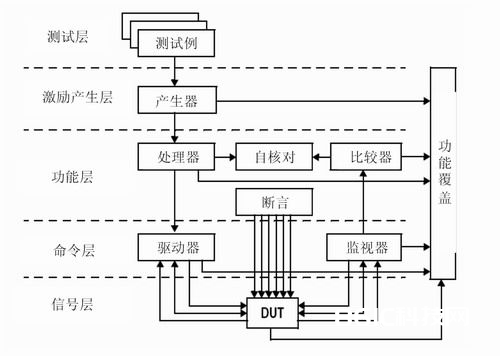

随着SoC设计日趋复杂,验证成为SoC设计过程中最关键的环节。本文介绍了Synopsys的RVM验证方法学,采用Vera硬件验证工具以及OpenVera验证语言建立目标模型环境,自动生成激励,完成自核

本文讨论电子系统级(ESL)设计和验证方法学在系统级芯片(SoC)设计中的应用。ESL设计是能够让SoC设计工程师以紧密耦合方式开发、优化和验证复杂系统架构和嵌入式软件的一套方法学,它还提供下游寄存器

随着SoC设计日趋复杂,验证成为SoC设计过程中最关键的环节。本文介绍了Synopsys的RVM验证方法学,采用Vera硬件验证工具以及OpenVera验证语言建立目标模型环境,自动生成激励,完成自核

本文讨论电子系统级(ESL)设计和验证方法学在系统级芯片(SoC)设计中的应用。ESL设计是能够让SoC设计工程师以紧密耦合方式开发、优化和验证复杂系统架构和嵌入式软件的一套方法学,它还提供下游寄存器