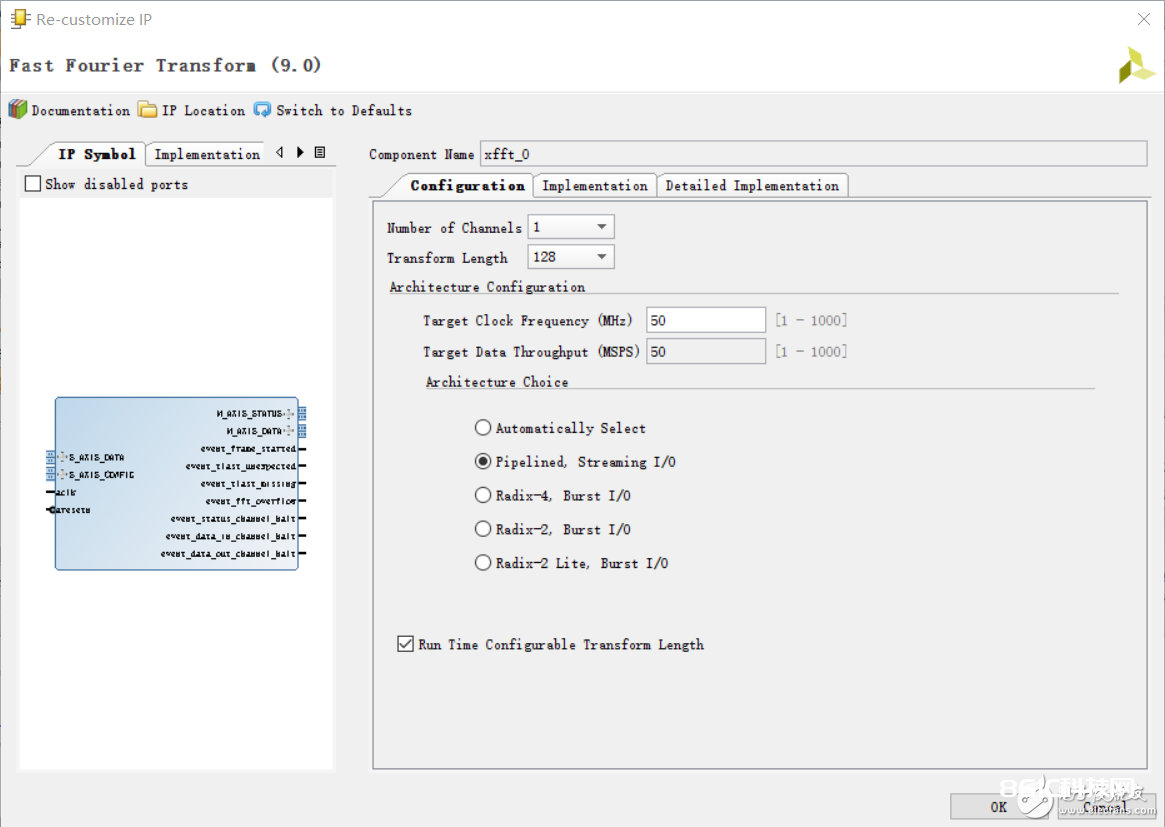

通过Xilinx FFT IP核的使用实现OFDM-由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。

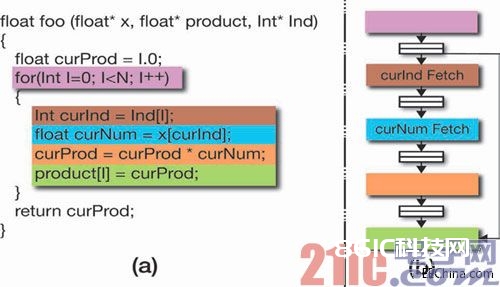

HLS优化设计中pipeline以及unroll指令:细粒度并行优化的完美循环-HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定的代码风格。展开 (unroll) 指令是只针对 for 循环的展开指令,和流水线指令关系密切,所以我们放在一起首先我们来看一下这三个指令在 Xilinx 官方指南中的定义: Unroll: Unroll for-loops to create multiple instances of the loop body and its instructions that can then be scheduled independently. Pipel

关于利用FPGA做图像处理的相关知识盘点-用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性。因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA。例如在一些分选设备中图像处理基本上用的都是FPGA,因为在其中相机从看到物料图像到给出执行指令之间的延时大概只有几毫秒,这就要求图像处理必须很快且延时固定,只有FPGA进行的实时流水线运算才能满足这一要求。

以FPGA为核心的高阶快速数字滤波器设计-本文详细讲述了通过Matlab工具设计FIR线性相位滤波器的方法, 并针对声波信号设计了优于传统结构的流水线CSD-DA结构, 该结构具有较明显的速度和面积优势。文中也通过仿真实验证实了设计的合理性和正确性。但值得指出的是, 该结构只适合固定滤波器系数的场合, 而如果要进行修改, 则需要重新对系数进行CSD编码和流水线分割。

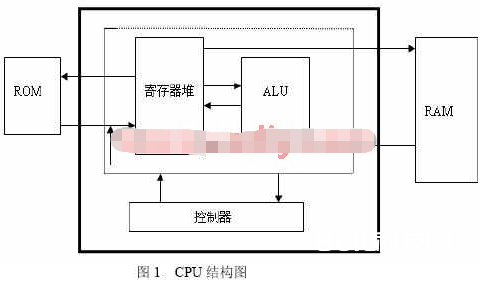

基于Xilinx Spartan II系列FPGA器件实现IP核的设计-精简指令集计算机RISC(Reduced Instruction Set Computer)是针对复杂指令集计算机CISC(Complex Instruction Set Computer)提出的,具备如下特征1)一个有限的简单的指令集; 2)强调寄存器的使用或CPU配备大量的能用的寄存器;3)强调对指令流水线的使用。

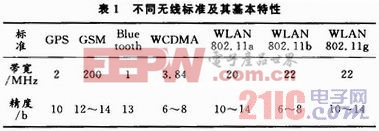

摘要:对多标准无线通信系统中的A/D转换器进行了研究,根据无线通信系统的特点,构建了一个新型可重构流水线A/D转换器结构,该A/D转换器的可重构功能是通过在低分辨率下关断子级流水线来实现的。转换器的系

Renesas(瑞萨电子)针对工业领域微控制器应用推出了RL78系列新产品R5F117BCGFP。该微控制器为16位MCU,采用CISC架构,具有三级流水线的,最高运行频率可达24MHz,结合其内部集

通过用于重构高级算法描述的简单流程,就可以利用高层次综合功能生成更高效的处理流水线。如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado设计套件