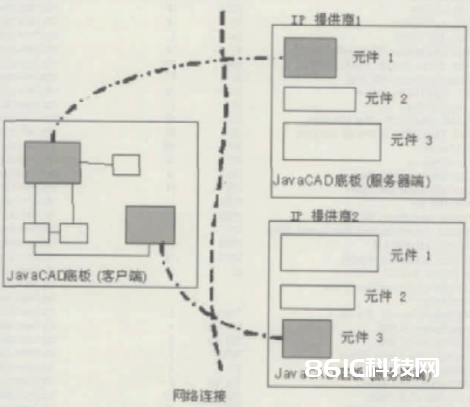

基于JavaCAD架构的安全性与IP保护研究-目前,基于IP的EDA设计流程面临着两大挑战。首先,必须提供方法技术,用于测试包含IP组件设计的可靠性和质量;另一方面,必须保护IP供应商和设计者的知识产权。第三方IP核的使用确实可以提高芯片设计效率,但是供应商将IP核交付到客户的过程却并非直截了当。对于客户来说,为了测试验证IP核,它必须具备一定的可见性。

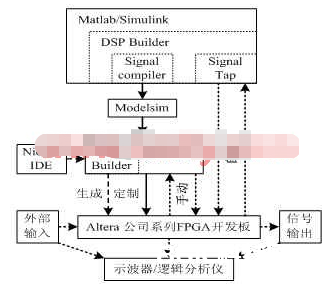

基于Cyclone系列FPGA器件和UART功能实现误码率测试仪器的设计-在通信系统的设计实现过程中,都需要测试系统的误码性能。而常见的误码率测试仪多数专用于测试各种标准高速信道,不便于测试实际应用中大量的专用信道,并且价格昂贵,搭建测试平台复杂。随着大规模集成电路的迅速发展,FPGA在保持其集成度高,体积小,功耗低,性价比高特性的同时,能够实现越来越复杂设计功能,日益广泛的应用于通信设备的设计实现。

采用LabVIEW FPGA的数据传输技术可确保数据传输的稳定性与可靠性-西安某汽车电子有限公司生产的XLM油泵支架产 品功能测试台设计中,有一项针对高度阻值(TSG)的 功能测试。该测试内容要求阻值电压采样与液位高度进 行一一对应。使用传统的采集方式难以保证采集的可靠 性。基予该设计要求,本文提出了一种采用LabVIEW FPGA的数据传输技术,该技术能够在高速采样的前提下确保数据传输的稳定性与可靠性。

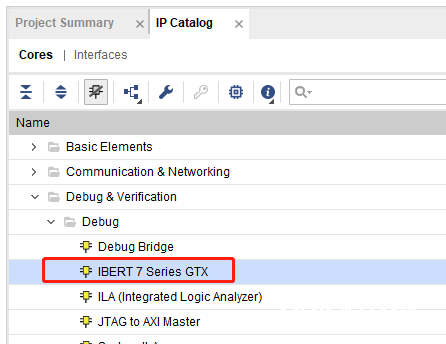

fpga开发板使用教程之在K7上用Ibert实现基本的GTX测试-GTX、GTH等具体是什么就不多介绍了,网上有很多。写这个的目的,就是当收到FPGA板卡后,要判断本板的高速串行总线是否能够应用,那就需要做基本的功能测试。我们可以用xilinx提供的ibert进行测试,而且基本上可以达到不用敲代码就可以完成测试的目的。 下面按步骤,一步一步实现。重点的地方我会标注出来。 (1)新建工程,只需选择好与板卡对应的FPGA型号即可,无须添加任何文件。 (2)添加ibert IP。 (3)配置IP: 这里我们先只配置一个quad,也

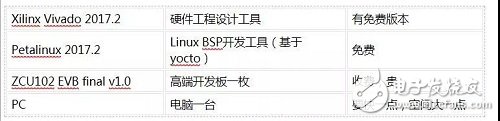

Zynq UltraScale+ MPSoC 上的多个Linux UIO设计-本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

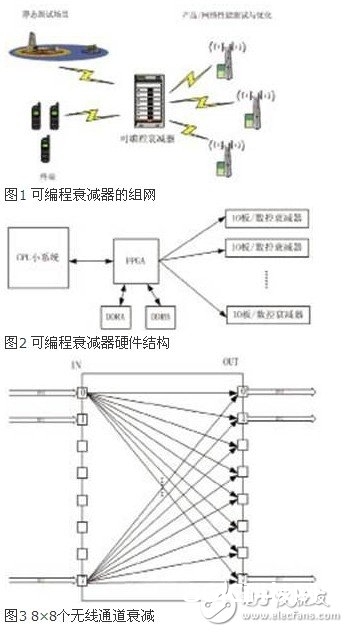

这种可编程衰减器最高可支持8×8输入输出的矩阵结构-可编程衰减器位于基站和终端之间,通过对射频信号的衰减控制,实现对无线信号的模拟,从而实现对测试场景的模拟。可编程衰减器提供多个数控接口,从小到大可以构建各个层次的测试网络。所构成的衰减矩阵通过模拟空口信道实现移动、切换、覆盖等多种测试项。

fpga开发板运用教程之在K7上用Ibert完成根本的GTX测验

fpga开发板运用教程之在K7上用Ibert完成根本的GTX测验