着重讨论基于FPGA的64点高速FFT算法的实现方法。采用高基数结构和流水线结构,大大提高了FFT处理器的运行速度。同时块浮点结构的引入,也大幅减少了浮点操作占用FPGA器件的资源数目,兼顾了FPGA

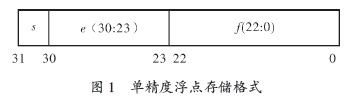

基于IEEE浮点表示格式及FFT算法,提出一种基2FFT的FPGA方法,完成了基于FPGA高精度浮点运算器的FFT的设计。利用VHDL语言描述了蝶形运算过程及地址产生单元,其仿真波形基本能正确的表示输

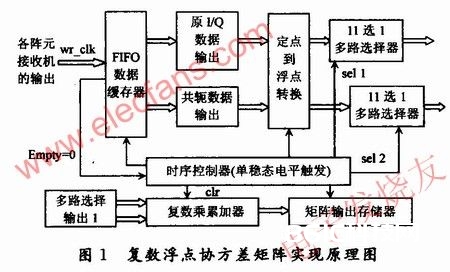

基于Altera浮点IP核实现浮点矩阵相乘运算时,由于矩阵阶数的增大,造成消耗的器件资源虽增加但系统性能反而下降的问题,针对现有IP核存在数据加载不连贯、存储带宽不均匀的不足,提出采用并行化数据存储、

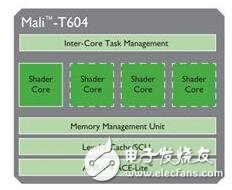

Mali GPU编程特性及二维浮点矩阵运算并行优化详解-本文针对Mali-T604 GPU论述了基于OpenCL的Linux平台上进行通用计算并行优化的方法,论述了Mali-T604 GPU的硬件特点

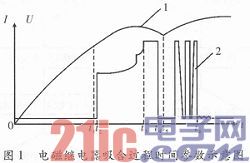

摘要 设计了一种基于新型浮点DSP—TMS320F28335的微型继电器测试系统,该系统通过内部A/D及外部采样电路对继电器线圈电流、触电电压和驱动电源电压的值进行实时采样,得到能反映继电