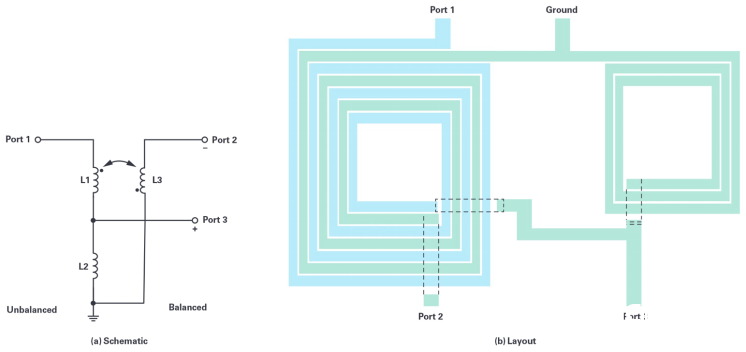

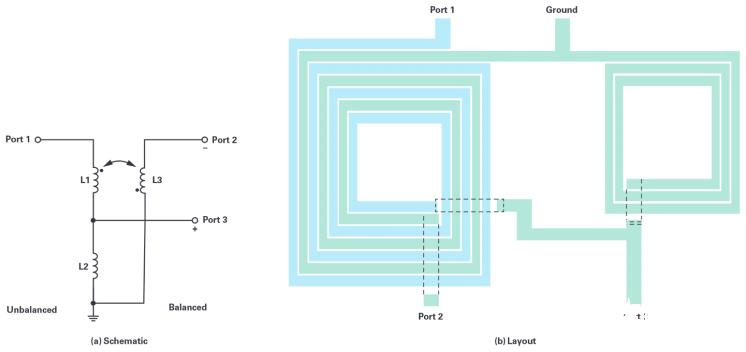

本文介绍仅需0 dBm LO驱动的宽带3 GHz至20 GHz SiGe无源混频器。新巴伦结构是实现宽RF带宽的关键创新。针对IF频段应用也采用相同的巴伦拓扑,支持300 MHz至9 GHz的宽IF。

基于Ruthroff型宽带巴伦结构实现双平衡混频器的设计-宽带混频器广泛应用于多功能无线收发器、微波收发器、微波回程、雷达和测试设备。宽带混频器使得在具有各种无线电参数的动态可编程性的无线电架构中使用单个混频器成为可能。

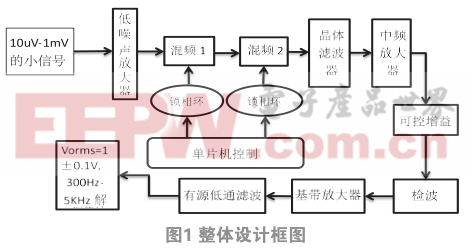

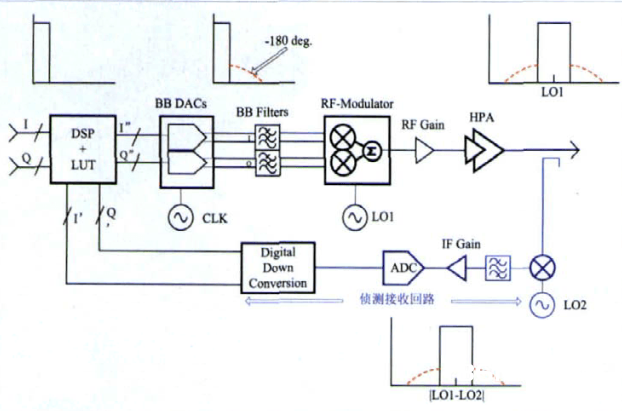

基于高线性混频器MAX9994实现侦测接收通道的设计方案-随着全球3G网络的大规模建设,运营商越来越注重降低CAPEX(建设成本)和OPEX(维护成本),功放作为基站当中最昂贵的器件之一,其对效率的要求越来越高,从而使得数字预失真DPD(Digital Pre-Distortion)技术得到飞快的发展。图1是功放数字预失真处理的基本结构框图。

利用运算放大器如何实现低频检相器或混频器的功能设计-一些运算放大器,比如AnalogDevices公司的AD8041和Intersil公司的EL5100,提供禁用引脚,它使人们能把数个运算放大器的输出并联用于视频多路传输。除了这种多路传输以外,人们还能用这种禁用功能把运算放大器配置作为检相器或混频器。图1描绘了禁用功能如何实现低频检相器。人们可以按相位参考信号的速率来开关该电路的放大器的增益。这么做会在运算放大器的输出端产生DC分量。该分量与输入信号的相位与参考信号的相位之间的相位差成正比。

将混频器功能与放大器集成实现电路调节变换增益-在很多应用中,频率变换级包括有一只缓冲器,最好还有一些额外的电压增益;一只混频器;还有一些滤波。你可以简单地将混频器功能与放大器集成起来,从而省掉混频器前的放大器。有种低价的实现办法是使用一只带掉电禁用功能的放大器。当用一个方波本振驱动禁用脚时,振荡器频率的方波将输入信号倍频,发生频率变换。