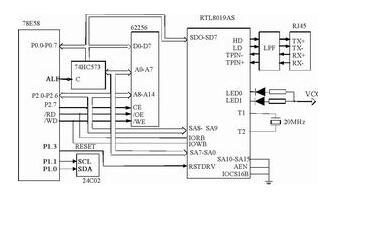

51单片机实现控制网卡芯片进行数据传输的设计-系统的硬件结构框图如图1所示。本系统的微控制器是Winbond公司的78E58,网络接口芯片是与NE2000系列兼容的ReaLTEk公司的RTL8019AS。RTL8019AS内置了10BASE-T收发器,外接一个隔离LPF滤波器,经RJ-45接口输出。外部RAM是62256,24C02是I2C总线的 EEPROM。

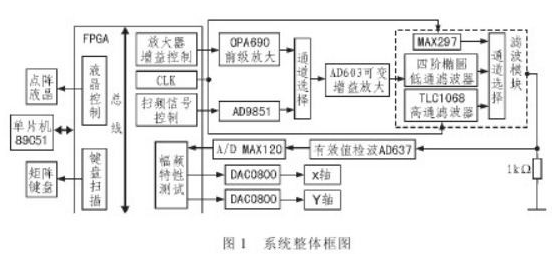

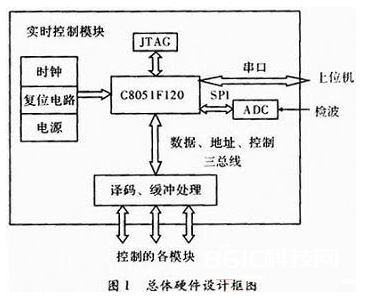

基于89C51单片机和FPGA结合的滤波器模块设计-滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。而对于程控滤波器,该系统的最大特点在于其滤波模式可以程控选择,且-3 dB截止频率程控可调,相当于一个集多功能于一体的滤波器,将有更好的应用前景。

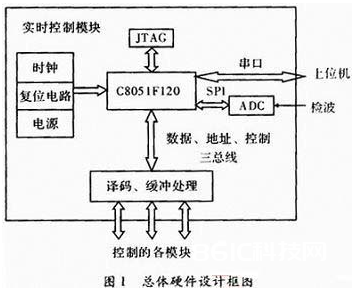

基于C51单片机的通信测试仪器设计-在该通信测试仪器中,实时控制模块主要实现对射频接收频综、射频发生频综、滤波器组件、射频输入模块、射频输出模块等实时控制作用。对射频检波信号进行A/D转换以获取数据。与上位计算机进行通信等功能。

基于C51单片机的通信测试仪器控制设计-在该通信测试仪器中,实时控制模块主要实现对射频接收频综、射频发生频综、滤波器组件、射频输入模块、射频输出模块等实时控制作用。对射频检波信号进行A/D转换以获取数据。与上位计算机进行通信等功能。

89C51单片机和FPGA为控制核心的程控滤波器设计-滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。

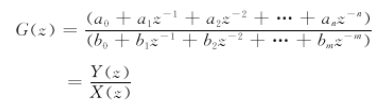

基于FPGA器件实现有限冲激响应滤波器的方案设计-一个模拟集成运算放大器可实现一个二阶滤波器,高阶滤波器可由二阶滤波器串联而成。然而,无源元器件实现滤波器的误差值为1.5%或更高,这需要提高元器件的性能。滤波器的典型的调试方法是不断的更换元器件值。而且,运算放大器要获得高的增益带宽,需要相位漂移保持最小或要保持闭环系统的稳定,这必然增加工程中实现滤波器的难度。

基于电路分割技术的查表法实现根升余弦脉冲成形滤波器FPGA设计-数字通信系统中,基带信号的频谱一般较宽,因此传递前需对信号进行成形处理,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。目前,数字系统中常使用的波形成形滤波器有平方根升余弦滤波器、高斯滤波器等。设计方法有卷积法或查表法,其中:卷积法的实现,需要消耗大量的乘法器与加法器,以构成具有一定延时的流水线结构。为降低硬件消耗,文献提出了一种分布式算法(Distributed Arithmetic,DA)的滤波器设计结构。它将传统的乘、累加运算转化为移位、累加运算,当运算数据的字宽较小时,极大地降低了硬件电路的复杂度,提高了响应速度;当运算数据的字长较长时,因其需要更多的移位迭代运算而不适合高速处理的需求。为此,文献提出了采用滤波器的多相结构与改进DA算法相结合的一种设

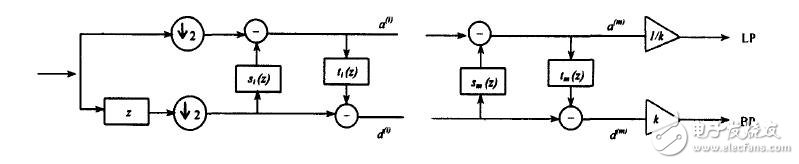

基于FPGA实现多种小波变换-基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有效地计算DWT。对于较长的滤波器,LS 的操作次数比滤波器组的操作方式减少将近一半,更适合硬件实现。