基可编程逻辑器件实现滤波器分组级联系统的设计-目前针对数字下变频,除了采用多片DSP组成并行处理模块外,一般都探索采用下变频处理的高效算法。本文针对这些高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。

系数源(Coefficient Source)支持哪五种滤波器类型?-(4)时钟频率(Clock Frequency ):此字段可以是整数或实数值。限制是根据采样频率,内插率和通道数设置的。该领域仅影响体系结构选择。最终的实现可能无法达到指定的时钟速率。

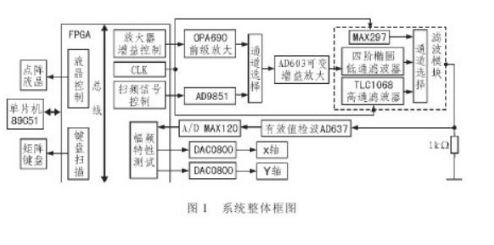

基于fpga和单片机的程控滤波器-以单片机和可编程逻辑器件(FPGA)为控制核心,设计了一个程控滤波器,实现了小信号程控放大、程控调整滤波器截止频率和幅频特性测试的功能。其中放大模块由可变增益放大器AD603实现,最大增益60dB,10dB步进可调,增益误差小于1%。程控滤波模块由MAX297低通滤波、TLC1068高通滤波及椭圆低通滤波器构成,滤波模式用模拟开关选择。本系统程控调整有源滤波的-3dB截止频率,使其在1~30kHz范围内可调,误差小于1.5%。此外,采用有效值采样芯片AD637及12位并行A/D转换器MAX120实现了对扫频信号幅度的测量。

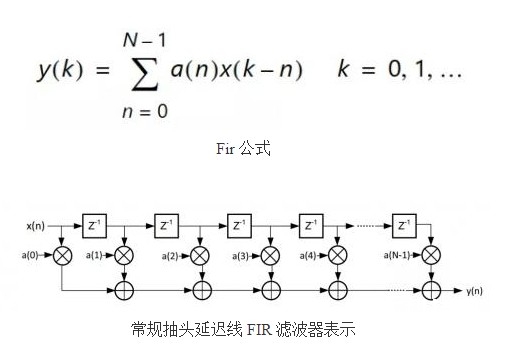

以FPGA为核心的高阶快速数字滤波器设计-本文详细讲述了通过Matlab工具设计FIR线性相位滤波器的方法, 并针对声波信号设计了优于传统结构的流水线CSD-DA结构, 该结构具有较明显的速度和面积优势。文中也通过仿真实验证实了设计的合理性和正确性。但值得指出的是, 该结构只适合固定滤波器系数的场合, 而如果要进行修改, 则需要重新对系数进行CSD编码和流水线分割。

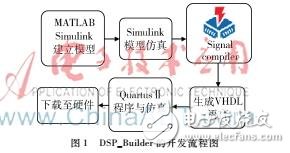

基于FPGA的可调FIR滤波器在实际通信系统中的实现方法设计- 基于灵活自适应的空口波形技术FOFDM(Filtered OFDM)是现代通信技术的研究热点,设计并实现可调FIR滤波器是实现该技术的核心工作之一。本文设计的基于FPGA的可调节FIR滤波器系数的自适应调整是通过控制算法对信道中的信号进行快速检测,然后将结果和滤波器的输出结果进行差值计算进行反馈调节。利用Quartus II和DSP Builder设计基于FPGA的16阶系数可调FIR滤波器,给出核心模块的设计电路图和仿真结果。仿真结果表明:基于灵活自适应空口波形技术可以在FPGA上实现,而且由于FPGA具有天然的并行性,实际的通信系统中可以采用并发模式进行,达到提高信号传送速率的目的。

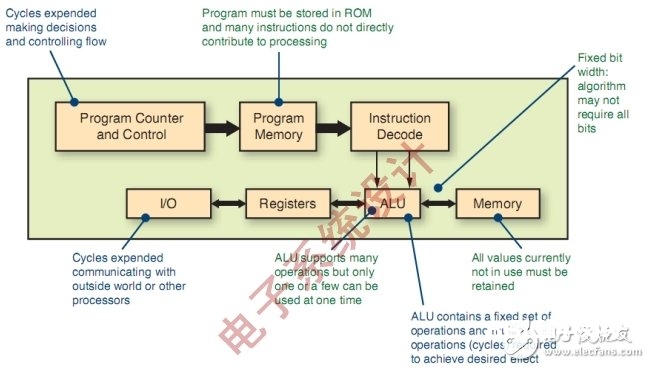

浅析FPGA和专用DSP的原理及应用-虽然定制实现DSP功能,但在很多应用中几种功能,如FIR(有限脉冲响应)滤波器,IIR(无限脉冲响应)滤波器、FFT(快速傅里叶)和混频器是共同的。所有这些功能都需要与加、减、累加一起的乘法单元组合。

如何利用FPGA技术来解决DSP的设计难题?-如果采用MAC模式,DSP48则非常适用,因为DSP48 Slice内含输入寄存器、输出寄存器和加法器单元。实现31抽头MAC引擎需要的资源包括一个DSP48、一个18kb块RAM(block RAM)和9个逻辑片。另外,还需要一些逻辑片用于采样、系数地址生成和控制。如果FPGA内置有600MHz的时钟,则在一个-3速度等级的Xilinx 7系列器件中,该滤波器能够以19.35MHz或1,935MS/s的输入采样速率运行。

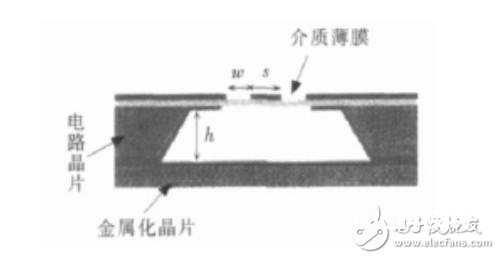

基于MEMS技术的微波滤波器研究进展-基于MEMS技术的滤波器是现在RF系统中的一个关键MEMS 器件。借助于MEMS 加工技术的进步及与射频/微波技术的结合,MEMS 滤波器的研究得到了快速的发展。MEMS 滤波器从RF 到毫米波段有很高的Q值、插入损耗低、线性好,适应现代日益复杂的RF 环境要求。##近年来由于微波、毫米波波段的多频段、宽带无线通信系 统的迫切需要,基于MEMS 技术的可调谐滤波器逐渐引起了人们很大关注。这种滤波器由MEMS 开关、共平面传输线、可变电抗元件等构成,它们具有低插入损耗,高线性度、高Q值和更好的三阶交调频率点功率性能。