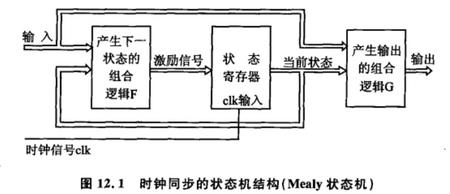

有限状态机是一种常见的电路,由于时序电路和组合电路组成,设计有限状态机的第一步是确定采用Moore状态机还是采用Mealy状态机。Mealy状态机的状态转变不仅和当前状态有关,而且和各输入信号有关;M

状态机设计是HDL设计里面的精华,几乎所有的设计里面都或多或少地使用了状态机的思想。状态机,顾名思义,就是一系列状态组成的一个循环机制,这样的结构使得编程人员能够更好地使用HDL语言,同时具有特定风格

通过减少寄存器间的逻辑延时来提高工作频率,或通过流水线设计来优化数据处理时的数据通路来满足高速环境下FPGA或CPLD中的状态机设计要求。本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优

当前以硬件描述语言为工具、逻辑器件为载体的系统设计越来越广泛。在设计中,状态机是最典型、应用最广泛的电路模块,其在运行速度的高效、执行时间的确定性和高可靠性方面都显现出强大的优势。状态机及其设计技术水

FPGA工程师:如何在FPGA中实现状态机?-安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类

说到单片机编程,不得不说到状态机,状态机做为软件编程的主要架构已经在各种语言中应用,当然包括C语言,在一个思路清晰而且高效的程序中,必然有状态机的身影浮现。灵活的应用状态机不仅是程序更高效,而且可读性

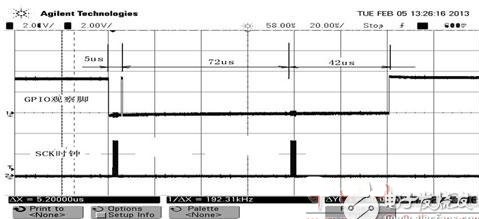

通过mmap方式应用程序在Linux下访问物理地址提高实时性-我们的一个项目中,系统由FPGA和ARM11结合为核心控制器,其中FPGA连接外部高速ADC、DAC和RF器件在ARM11的控制下,实现GB18000-6C标准的UHF RFID读写控制状态机。FPGA与ARM11的接口采用SPI,其中ARM11选用三星S3C6410,作为SPI的主机,FPGA作为SPI的从机,受S3C6410的控制。在本系统中,SPI接口充当ARM11和FPGA交互的桥梁,ARM11的命令和动作参数传给FPGA并启动FPGA处理状态机,FPGA动作的结果也通过SPI回传给ARM11,两者之间的通讯效率在系统中需要重点关注。