一种基于ARM和FPGA的线阵CCD在线测量线缆系统设计剖析-近几年来,电线、电缆、光纤等产品的需求量大大增加,外径尺寸的质量控制成为许多生产厂家急需解决的问题。传统的测试手段有以下几种:(1)手工测量法:采取先加工后测量的方法,精度一般,人为因素多,劳动强度大,信息反馈慢,直接影响了线材的质量和生产效益。(2)接触法测量:精度较高,但易磨损,重复测量精度差。(3)光电二极管阵列测量法:速度快,易处理,但精度差。因此,必须有一套高精度的实时在线检测系统,一方面可使生产人员及时了解线径的大小及偏差,另一方面给生产机构伺服系统提供正比于偏差的反馈量,实现反馈控制。以线阵CCD高精度传感器为核心组成的动态外径测量仪器具有速度快、精度高、抗干扰能力强等优点,成为最为理想的工业在线检测手段之一。

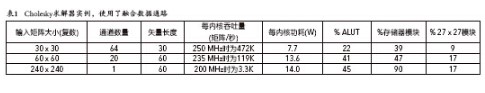

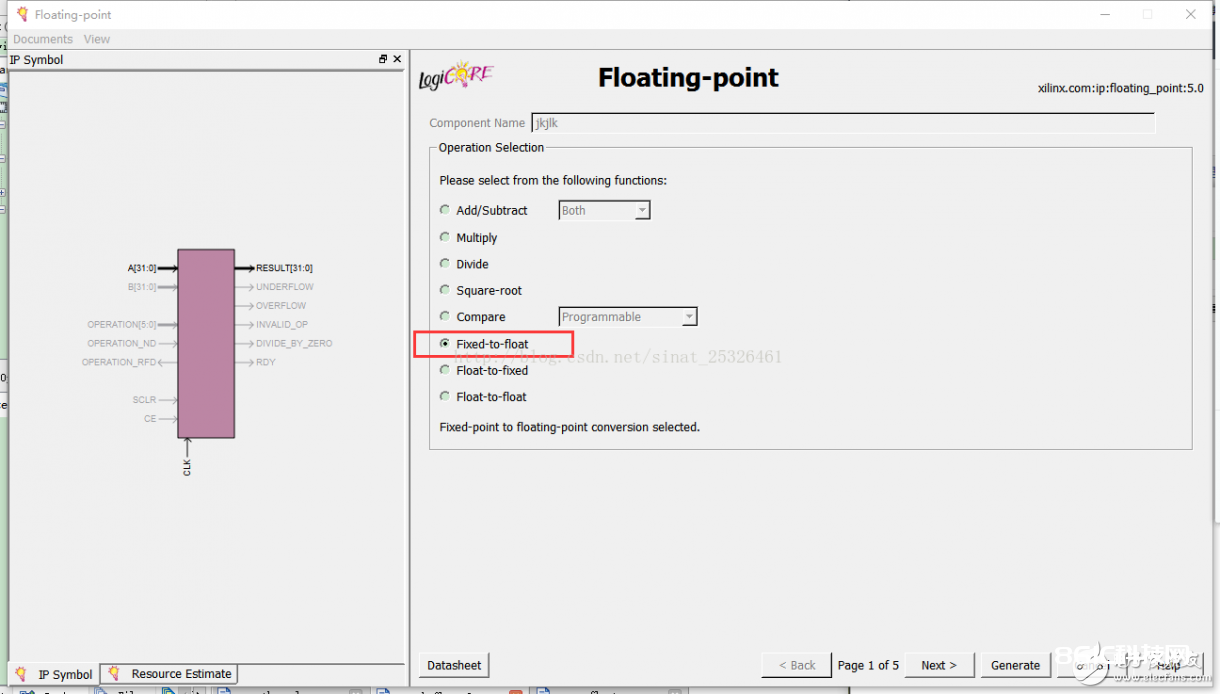

Xilinx Vivado HLS中Floating-Point(浮点)设计介绍-尽管通常Fixed-Point(定点)比Floating-Point(浮点)算法的FPGA实现要更快,且面积更高效,但往往有时也需要Floating-Point来实现。这是因为Fixed-Point有限的数据动态范围,需要深入的分析来决定整个设计中间数据位宽变化的pattern,为了达到优化的QoR,并且要引入很多不同类型的Fixed-Point中间变量。而Floating-Point具有更大的数据动态范围,从而在很多算法中只需要一种数据类型的优势。Xilinx Vivado HLS工具支持C/C++ IEEE-54标准单精度及双精度浮点数据类型,可以比较容易,快速地将C/C++ Floating-Point算法转成RTL代码。

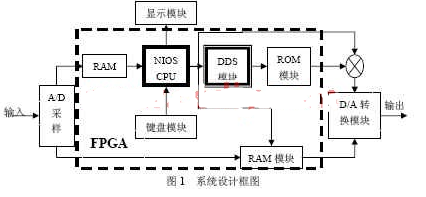

基于VHDL语言及SOPC技术实现全数字调频信号发生器的设计-在常用的信号源及信号处理设计方案中,RC/LC振荡电路频率调整方便,但是它的工作频率稳定度较低。频率稳定度较低导致系统的工作稳定度降低,使其不适用于对精度要求较高的场合。晶振具有稳定且较高的频率,其频率稳定精度可达到10-6以上,但是它的频率是固定不可调的。晶振不能很方便地产生各种频率可变的信号。

Altera FPGA硬核浮点DSP模块解决方案提高运算性能-以往FPGA在进行浮点运算时,为符合IEEE 754标准,每次运算都需要去归一化和归一化步骤,导致了极大的性能瓶颈。因为这些归一化和去归一化步骤一般通过FPGA中的大规模桶形移位寄存器实现,需要大量的逻辑和布线资源。通常一个单精度浮点加法器需要500个查找表(LUT),单精度浮点要占用30%的LUT,指数和自然对数等更复杂的数学函数需要大约1000个LUT。因此随着DSP算法越来越复杂,FPGA性能会明显劣化,对占用80%~90%逻辑资源的FPGA会造成严重的布线拥塞,阻碍FPGA的快速互联,最终会影响时序收敛。

浅谈AD8205的传感器内部电路结构及其工作原理-在许多工业应用中,都需要在高共模电压情况下检测小差分电压,以实现对电流的监控。但在高共模电压情况下,输出电流的检测电路比较复杂,而且精度难以保证。采用新型高侧电流传感器AD8205可以简化其检测电路,并能大大提高其检测和控制的精度。

ADI热电偶丈量计划

ADI热电偶丈量计划