基于AIS系统中2189M的硬件设计-ADSP2189M芯片是一种定点DSP,其指令周期为13.3ns,运行速度可达75MIPS。处理器包括算术/逻辑单元(ALU),乘法/累加器(MAC)和桶状移位器。存储器采用哈佛结构,有48K的PRAM和32K的DRAM。两个SPORT同步串口,一个定时器以及主机接口可以和主机处理器直接相连。DMA接口包括内部DMA接口(IDMA)和字节DMA接口(BDMA)。

MCS-51单片机的算术运算指令解析-MCS-51有一个程序状态字寄存器PSW,用来保存指令执行结果的标志,供程序查讯和判别。PSW是特殊功能寄存器中的一个,其格式如下:

PSW7--既是布尔处理机的累加器C,又是进位标志CY,如果操作结果在最高位有进位输出(加法时)或借位输入(减法时),置位CY,否则清“0”CY。

AC--辅助进位(半进位)标志。如果操作结果的低4位有进位(加法时)或向高4位借位时(减法),置AC,否则清“0”AC,AC主要用于二-十进制数加法调整。

51单片机加1指令的应用方法解析-INC A;(A)+1→(A) 累加器A中的内容加1,结果存在A中

INC data;(data)+1→(data) 直接地址单元中的内容加1,结果送回原地址单元中

INC @Ri;((Ri))+1→((Ri)) 寄存器的内容指向的地址单元中的内容加1,结果送回原地址单元中

INC Rn;(Rn)+1→(Rn)寄存器Rn的内容加1,结果送回原地址单元中

INC DPTR;(DPTR)+1→(DPTR)数据指针的内容加1,结果送回数据指针中

用途很简单,就是将后面目标中的值加1。

8051单片机指令系统的7种寻址方式解析-寄存器寻址:寄存器寻址就是操作数在寄存器中,因此指定了寄存器就得到了操作数。采用寄存器寻址方式的指令都是一字节的指令,指令中以符号名称来表示寄存器。例如:MOV A R1 这条指令的功能是把工作寄存器R1的内容传送到累加器A中,由于操作数在R1中,因此指令中指定了R1,也就得到了操作数。

单片机累加器A的逻辑操作方法介绍-CLR A ;将A中的值清0,单周期单字节指令,与MOV A,#00H效果相同。

CPL A ;将A中的值按位取反

RL A ;将A中的值逻辑左移

RLC A ;将A中的值加上进位位进行逻辑左移

RR A ;将A中的值进行逻辑右移

RRC A ;将A中的值加上进位位进行逻辑右移

8051单片机CPU的内部组成及功能介绍-运算器以完成二进制的算术/逻辑运算部件ALU为核心,再加上暂存器TMP、累加器ACC、寄存器B、程序状态标志寄存器PSW及布尔处理器。累加器ACC是一个八位寄存器,它是CPU中工作最频繁的寄存器。在进行算术、逻辑运算时,累加器ACC往往在运算前暂存一个操作数(如被加数),而运算后又保存其结果(如代数和)。

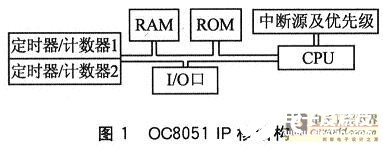

基于OC8051IP核的仿真调试方案在FPGA中实现下载测试-OpenCores网站提供的OC8051 IP核与8051的系统结构相同,如图1所示。该IP核兼容所有8051指令系统,内部资源包括:8位CPU,寻址能力达2×64K;4 KB的ROM和128字节的RAM;4个8位I/O口;16位内部定时/计数器;5个中断源和2个中断优先级。采用Verilog语言对其各个模块进行描述。系统主要模块及其功能说明如表1所列。不同模块对应的源文件均是以模块名称命名的,例如累加器A对应的源文件为oc8051_acc.v。

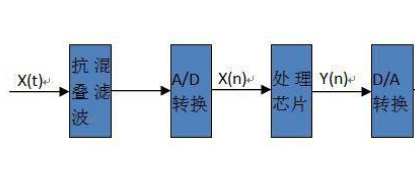

简析DSP的工作原理-DSP内部除了算术逻辑单元(ALU),还包括多个处理单元——辅助寄存器运算单元(ARAU),累加器(ACC),硬件乘法器(MULT),以及丰富的总线资源,它们的存在使得DSP可以拥有一些数字信号处理的特殊DSP指令,以及可以快速的访问存储以及并行操作的能力,保证数字信号处理中的实时的高速度、高精度累加即乘法等运算。