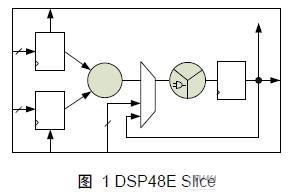

基于Adaboost算法结合Virtex5平台如何提升FPGA器件的性能-本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25×18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。

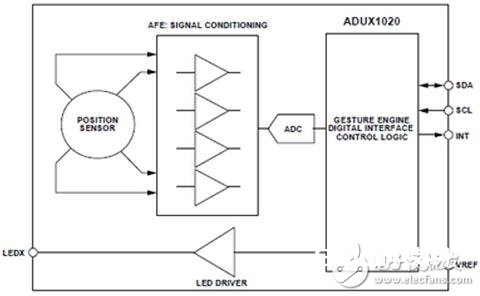

14位模数ADC+20位突发累加器的ADI手势识别传感器方案-ADI公司的ADUX1020是集成了14位模数转换器(ADC)和20位突发累加器的高效率光度传感器,采用单点检测改善了应用的可靠性,同时所需元件数更低,因而为系统开发人员降低了设计复杂性和成本;同时还具有高环境光抑制能力,可在恶劣的光照条件下提供可靠而精确的操作.1.8 V模拟/数字内核,主要用在便携式设备中的用户接口(UI)控制手势。

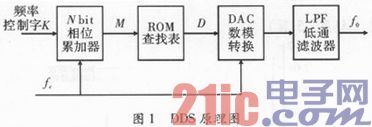

摘要 基于直接数字频率合成技术DDS的原理,分析了影响DDS频率输出的核心因素。在此基础上仿真验证了相位累加器的位数对DDS频率输出的作用。介绍了一种DDS芯片AD9852并基于这种芯片提出了一种雷达