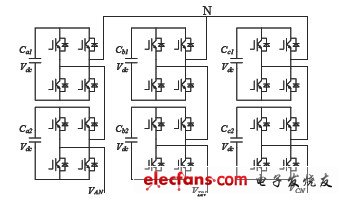

基可编程逻辑器件实现滤波器分组级联系统的设计-目前针对数字下变频,除了采用多片DSP组成并行处理模块外,一般都探索采用下变频处理的高效算法。本文针对这些高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。

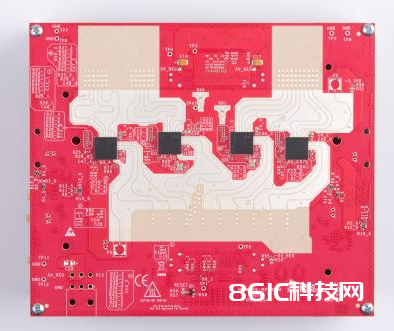

成像雷达传感器的特点及原理解析-成像雷达由一个传感器配置启用,其中多个低功率TI毫米波传感器级联在一起,且作为一个单元同步运行。它具有多个接收和发射通道,能够显著提高角分辨率和雷达距离性能。当毫米波传感器级联在一起时,可以使用集成移相器来创建波束赋形,从而达到400米的扩展范围。图1显示了评估模块上的级联毫米波传感器及其天线。

成像雷达传感器在自动驾驶汽车中的应用解析-成像雷达由一个传感器配置启用,其中多个低功率TI毫米波传感器级联在一起,且作为一个单元同步运行。它具有多个接收和发射通道,能够显著提高角分辨率和雷达距离性能。当毫米波传感器级联在一起时,可以使用集成移相器来创建波束赋形,从而达到400米的扩展范围。图1显示了评估模块上的级联毫米波传感器及其天线。

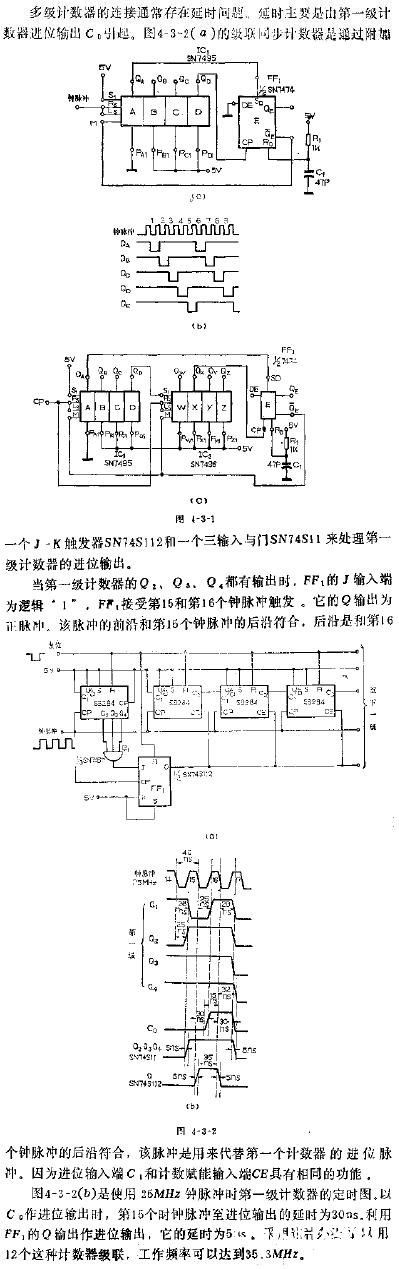

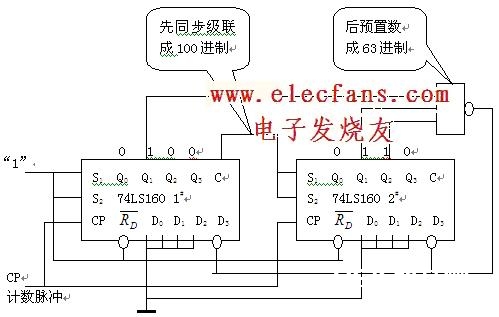

先级联后预置数构成的63进制计数器:我们同样也可以先用级联法组成10i计数器、或16i计数器,再用预置数法组成任意进制计数器。63进制计数器,可以先用两片10进制计数器(74LS160)组成100进制

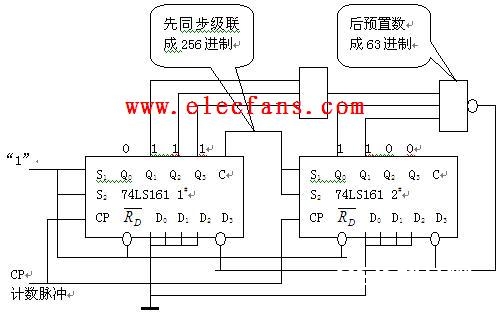

用16进制计数器先级联后预置数构成的63进制计数器:若先用16进制计数器级联,同样还是实现63进制计数器,我们也可以先用16进制计数器两片级联成16×16=256进制计数器,再用预置数法组成63进制计