FSMC如何读写CPLD-STM32 通过 FSMC 读写CPLD 的程序,CPLD挂在STM32的地址线和数据线上,将CPLD看做片外RAM的方式来进行读写,在我做的板子上CPLD挂在第四个区,因此基地址是0x6c000000,通过FSMC来进行读写,程序较为简单,具体的地方在函数中都有注释,仅供参考。

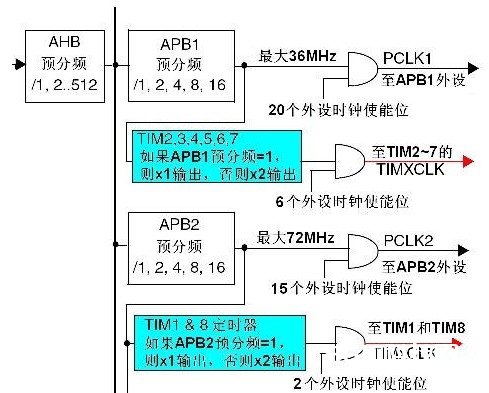

STM32单片机定时器的时钟源设置-名为TIMx的有八个,其中TIM1和TIM8挂在APB2总线上,而TIM2-TIM7则挂在APB1总线上。其中TIM1&TIM8称为高级控制定时器(advanced control timer)。他们所在的APB2总线也比APB1总线要好。APB2可以工作在72MHz下,而APB1最大是36MHz。

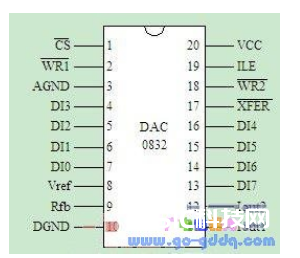

51单片机与DA转换器的应用-D/A转换器与单片机接口方便与否,主要决定于转换器本身是否带数据锁存器。有两类D/A转换器,一类是不带锁存器的,另一类是带锁存器的。对于不带锁存器的D/A转换器,为了保存来自单片机的转换数据,接口时要另加锁存器,因此这类转换器必须在口线上;而带锁存器的D/A转换器,可以把它看作是一个输出口,因此可直接在数据总线上,而不需另加锁存器。

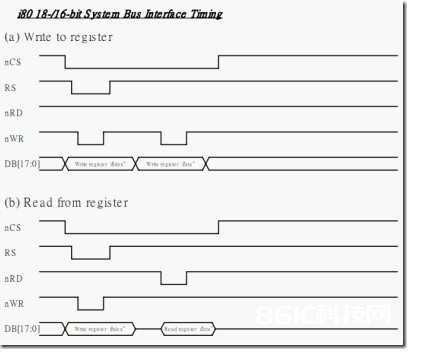

AVR单片机与CPLD的通信设计-项目中需要使用CPLD完成一部分算法设计,参数由AVR给出,因此需要完成AVR和CPLD的通信。因此写了一个测试程序。CPLD挂在AVR的数据和地址总线上,AVR使用ATmega128,在CPLD中设置几个寄存器,通过AVR读写寄存器来实现两者之间的通信。

MCU时钟设计方案-两个时钟频率可以彼此完全无关,或者它们可以是彼此的倍数。在任何一种情况下,都有可能在切换时在时钟线上产生毛刺。时钟线上的毛刺对整个系统是危险的,因为它可能被某些寄存器解释为捕获时钟边沿而被其他寄存器忽略。

单片机系统不正常工作了该如何处理-查单片机,看看管脚有没有问题;一般编程器能够将程序写入,说明单片机是好的;最好手头上准备一个验证过的单片机,内部有一个简单的程序,比如,在某个口线上输出1个1秒占空比的方波等,可以使用万用表测量。

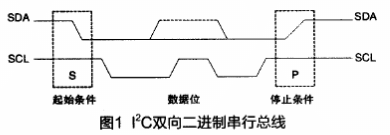

Core I2C的原理及采用FPGA技术实现I2C IP核的设计-I2C(Inter Integrated Circuit)双向二线制串行总线,是由飞利浦公司制定的。I2C总线是一个多主机的总线,使用串行数据线(SDA)和串行时钟线(SCL)在总线上传递信息。每个器件都有一个唯一的识别地址,而且都可以作为一个发送器或接收器。当连接在I2C总线上的多个主机器件同时传输数据时,通过仲裁来避免冲突。SDA和SCL都是双向线路,通过一个电流源或上拉电阻连接到电源。器件输出级必须是漏极开路或集电极开路,当总线空闲时,两条线路处于高电平,执行线与的功能。