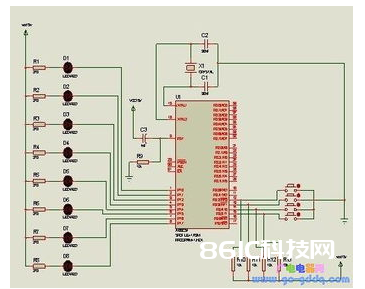

基于MCS-51单片机的彩灯控制程序设计-1.程序结构采用主程序和中断服务子程序结构

2.定时中断程序,并行口输出,控制彩灯移动

定时器0于方式1,16位,10ms中断一次

40H10ms计数单元

41H初值为01101101B

51单片机属于哈佛结构还是冯氏结构-哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储 器中读取数据,并进行下一步的操作(通常是执行)。

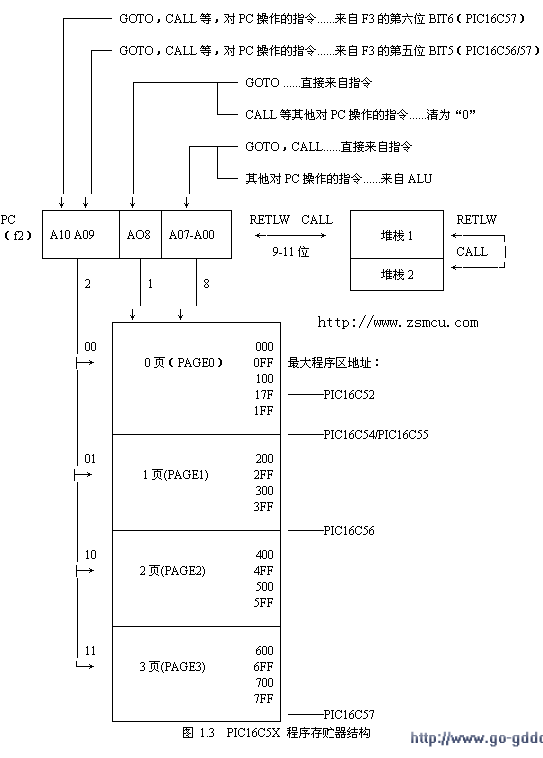

PIC16C5X单片机的程序存储器结构和堆栈技术介绍-从上图可看出,PIC程序存储器采用分页结构,每页长0.5K。因此对于PIC16C52程序存储器在1页之内,而对于PIC16C54和PIC15C55程序存储器容量为1页,PIC16C56和PIC16C57 的容量则分别为2页和4页。

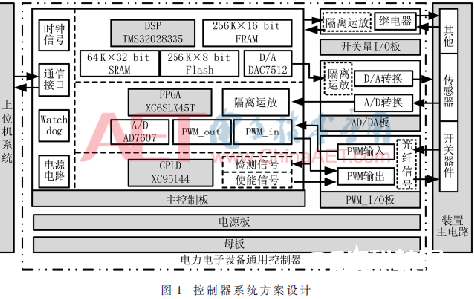

一种DSP+FPGA+CPLD通用型控制器设计方案介绍-随着电力电子技术的不断发展以及工业用电设备对电能质量需求的不断提高,越来越多的复杂拓扑结构、大容量系统、高安全稳定性的电力电子设备得到研究并应用到众多实际工程实践。针对多种电力电子拓扑结构不同工程应用实际,其相应的控制、保护系统同样越来越趋于复杂化和多样化。先进处理器的控制系统是现代电力电子设备的核心部件[1-3],以 DSP 为代表的传统处理器控制系统在中低压电力电子设备控制和保护中已有广泛的应用,并且取得了良好的控制效果。但在高压大功率电力电子设备控制系统的应用上,传统 DSP 控制器还存在不足。首先是 AD 采样通道和 PWM 信号输出通道数量有限,难以满足拓扑结构复杂的大功率电力电子设备的检测和控制要求;其次是由于 DSP 芯片在运行中复位在所难免,复位期间无法对电力电子设备进行有效控制与

AVR单片机的主要特性及应用解析-AVR单片机硬件结构采取8位机与16位机的折中策略,即采用局部寄存器存堆(32个寄存器文件)和单体高速输入/输出的方案(即输入捕获寄存器、输出比较匹配寄存器及相应控制逻辑),提高了指令执行速度,克服了瓶颈现象,增强了功能;同时又减少了对外设管理的开销,相对简化了硬件结构,降低了成本。

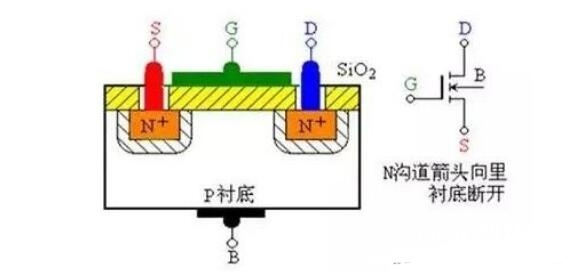

本站为您提供的什么是MOS管?MOS管结构原理图解(应用_优势_三个极代表),本文首先介绍了mos管的概念与mos管优势,其次介绍了MOS管结构原理图及mos管的三个极判定方法,最后介绍了MOS管(场效应管)的应用领域及它的降压电路。

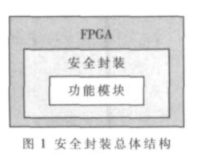

基于FPGA技术实现安全封装双向认证方案的设计-在深入分析基于FPGA的安全封装结构的基础上,针对其实际应用中身份认证的安全性要求,重点研究并设计了一种适用于FPGA安全封装结构的身份认证模型。该模型通过利用RSA公钥密码算法和SHA-1算法,实现了对用户及FPGA的双向认证。该模型具备良好的可移植性和安全性,能够有效抵御多种攻击,为基于FPGA的安全封装应用提供了强有力的用户权限认证。

基于EP2S60型FPGA芯片的LDPC码快速编码的实现设计-低密度奇偶校验(Low Densitv Paritv Check,LDPC)码已成为当今信道编码领域的研究热点之一。LDPC码属于线性分组码,根据其构造方法和相应的编码算法,主要分为两类:一类是随机构造的LDPC码,该类码在长码时具有很好的纠错能力,然而由于码组过长,以及生成矩阵与校验矩阵的不规则性,使编码过于复杂而难以用硬件实现,编码时间过长也不利于硬件的实时应用;另一类是结构码,它由几何、代数和组合设计等方法构造。大多数LDPC结构码是循环或准循环结构,准循环码在中短码时具有相当强的纠错能力,性能接近随机构造的最优LDPC码,又因其硬件实现极其简单,只需用反馈移位寄存器连接就可实现,因此具有很好的应用前景。

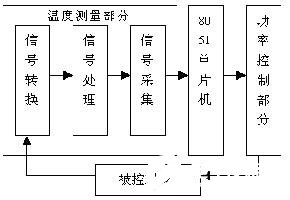

采用CPLD器件MAX7128实现温度控制系统的应用设计-“温度”是各类工业控制生产中常见的、而又十分重要的控制参数。人们研制出各种针对不同控制对象的温度自动控制系统,其中软件控制算法已比较成熟,但温度控制系统的硬件构成特别是功率控制部分往往存在着硬件结构复杂,分离元件较多,结构较为封闭等问题。随着CPLD器件的大规模运用,采用CPLD器件可简化控制系统的硬件结构。本文设计了一种以8051单片机为核心的温度控制系统,该系统的控制部分由CPLD来完成,针对不同的控制对象可采用不同的控制算法,因此该控制系统具有结构开放、成本低廉、性能可靠等特点。