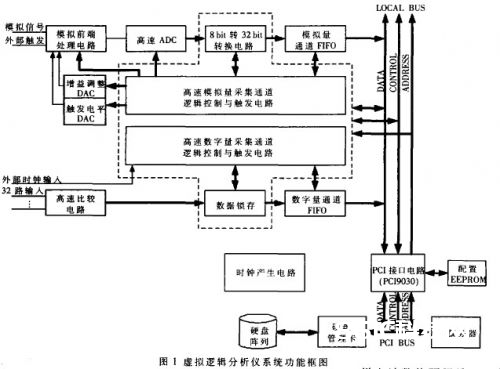

提出了一种基于FPGA的虚拟逻辑分析仪的设计。该系统对采集到的模拟或数字信号进行存储、处理和逻辑分析。通过FPGA控制数据单次或连续采集、缓冲,通过PCI总线将缓冲区数据转移到硬盘管理卡,由硬盘管理卡

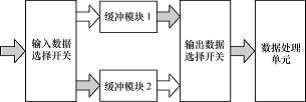

输入的数据经过选择开关后,分别进入缓冲模块1和缓冲模块2。当数据写入缓冲模块1的时候,数据处理单元从缓冲模块2读取数据进行处理;当数据写入缓冲模块2的时候,数据处理单元从缓冲区模块1读取数据进行处理。

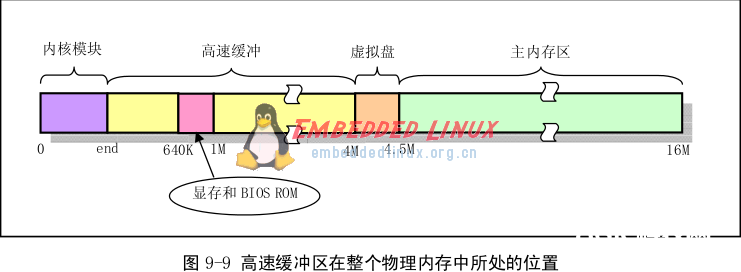

Linux0.11-缓冲区初始化-memory_end = (1<<20) + (EXT_MEM_K<<10);memory_end &= 0xfffff000;if (memory_end > 16*1024*1024)memory_end = 16*1024*1024;if (memory_end > 12*1024*1024) //内存>12M 设置高速缓冲区大小4Mbuffer_memory_end = 4*1024*1024;else if (memory_end > 6*1024*1024)// 内存>6M 设置高速缓冲区大小2Mbuffer_memory_end = 2*1024*1024;elsebuffer_memory_end = 1*1024*1024;//否则设置高速缓冲大小1Mmain_memory_start = buffer_memory_end;#ifdef RAMDISKmain_memory_start += rd_init(main_memory_start, RAMDISK*1024);#endif