五个方面看M级处理器在IOT领域中的运用-MIPS M级系列产品可以高速运行,一些CPU配置都配备了完整的MMU(内存管理单元)以及指令和数据缓存控制器。M级处理器具有运行RTOS(实时运行系统)和完

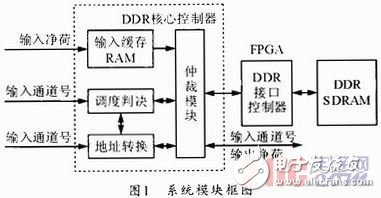

基于MIMO技术的视频缓存器设计方案-随着高速处理器的不断发展,嵌入式系统应用的领域越来越广泛,高速大容量缓存器被广泛应用于音视频系统中,然而专用的高速大容量缓存芯片价格过于昂贵,传统SDRAM在带宽上已经逐渐无法满足应用要求,特别是对于多路数据多进多出时,两者都无法很好的满足要求,这里提出一种利用双沿随机动态存储器(DDR SDRAM)结合外加专用电路的设计方案。

三维图像处理系统组成及实现方案-激光带预处理算法的实现[2]为:由于有激光帧和无激光帧是依次交替产生的,因此首先要保存一帧有激光帧,在其下一帧,即无激光帧到来时,将保存的有激光帧和当前无激光帧的相同行、列的点相减,再对结果进行亮度提取,处理完成后的数据存入目标缓存。

什么是Web缓存,HTTP缓存和浏览器缓存的区别-前端缓存主要是分为HTTP缓存和浏览器缓存。其中HTTP缓存是在HTTP请求传输时用到的缓存,主要在服务器代码上设置;而浏览器缓存则主要由前端开发在前端js上进行设置。

基于FIE8100 SoC平台实现Linux软件开发套件的设计-FA526是一颗有着广泛用途的32位RISC处理器。它包括一个同步CPU内核(core)、独立的指令/数据缓存(cache)、独立的指令/数据暂存器(scratchpads)、一个写缓存(write buffer)、一个内存管理单元(memory management unit)和JTAG在线仿真(ICE)接口。CPU内核是6级流水线(pipeline)的哈佛(Harvard)结构,包括取指令(fetch)、解码(decode)、搬移(shift)、执行(execution)、数据访存(memory)、写回(write)等。为了提高整体性能,FA526 CPU还包含了一个分支运算缓存(Branch Target Buffer:BTB),故可减少分支运算的开销(penalties)。