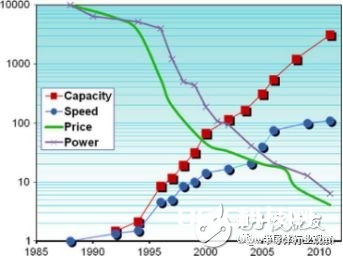

浅谈现场可编程门阵列发展三个阶段的驱动压力和基本特征-自引入以来,现场可编程门阵列(FPGA)的容量增加了10000倍以上, 性能增加了100倍。 单位功能的成本和功耗都减少了超过1000倍。 这些进步是由工艺缩放技术所推动的, 但是 FPGA 的故事比简单缩放技术的更复杂。 摩尔定律的数量效应推动了FPGA在体系结构、应用和方法方面发生质的变化。 因此, FPGA 已经经历了几个不同的发展阶段。 本文分别总结了发明、扩张、累积这三个阶段, 并讨论了它们的驱动压力和基本特征。 本文最后展望了未来的FPGA阶段。

如何利用FPGA硬件实现固定倍率的图像缩放?-近年来,FPGA技术发展迅速,片内集成了PLL、硬件乘法器、存储器,具有了实现优秀算法的充足资源。许多航空电子嵌入式图像处理系统是由固定的视频源和显示设备组成,系统中图像缩放的倍率是固定的。文中针对此展开重点研究,基于FPGA硬件,实现固定倍率的图像缩放。

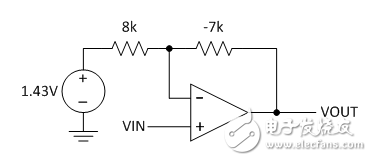

TPS62200可调式降压型转换器实现动态电压缩放技术电路图OMAP1510处理器具有两种操作模式:AWAKE(唤醒)模式以及低功耗的DEEP-SLEEP(深睡眠)模式。在AWAKE模式时,OMAP1

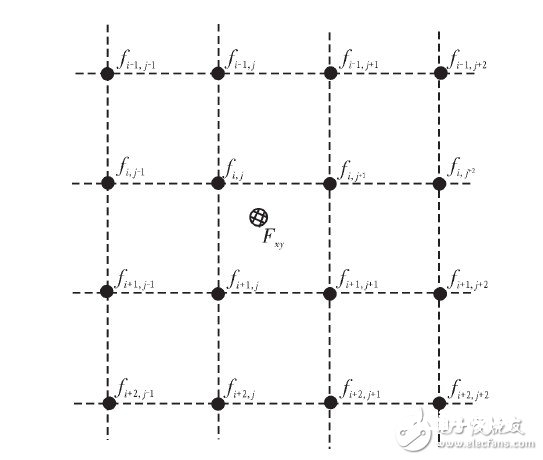

基于FPGA硬件实现固定倍率的图像缩放,将2维卷积运算分解成2次1维卷积运算,对输入原始图像像素先进行行方向的卷积,再进行列方向的卷积,从而得到输出图像像素。把图像缩放过程设计为一个单元体的循环过程,