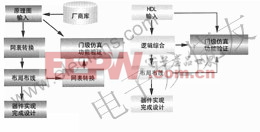

在Protel99SE开发软件中实现FPGA/CPLD系统的设计-在Protel99se嵌套的PLD99的开发环境下,可编程逻辑器件设计可以直接面向用户要求,自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成能够下载到器件的JED文件,该方法结构严谨,易于操作,其设计流程如图1所示。

2020新年伊始,一场突如其来的疫情,让整个中国陷入沉寂。各行各业,自上而下积极响应居家隔离的要求。为保证工作与学习不被耽误,云办公、线上教学模式开启。与此同时,大量的数据信息在网络中传输,如何确保这

天下熙熙皆为利来,天下攘攘皆为利往,名利二字,道尽人生大半,在一个“齐心一致向钱看”的时代,大学老师亦不能免俗。面对学校自上而下的各项考核,很多大学老师上午教课,下午写本子,晚上搞科研,过的也是996

在Protel99SE开发软件中实现FPGA/CPLD系统的设计-在Protel99se嵌套的PLD99的开发环境下,可编程逻辑器件设计可以直接面向用户要求,自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成能够下载到器件的JED文件,该方法结构严谨,易于操作,其设计流程如图1所示。