新建STM32工程全局声明两个宏的原因-在uVision中新建STM32工程后,需要从STM32标准库中拷贝标准外设驱动到自己的工程目录中,此时需要在工程设置->C/C++选项卡下的Define文本框中键入这两个全局宏定义。

单片机的红外解码程序设计-我照着原子的移植,我用的是自己的延时,也就是系统定时器,MTD,单步调试的时候,发现居然死在了systick那里,进不了中断,一步步观察,好像导致进不了中断的原因就是:我已经进了外部中断,心想,没道理啊,系统定时器的优先级不应该是高于外部中断的么,因为他是核决定的呀(至少我是这么想的),然后又查了相关资料,据说系统定时器的中断优先级是最低的,这时候我才恍然大悟!

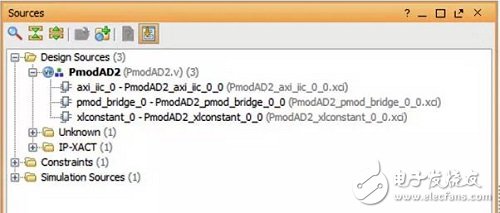

没有直接可用的Pmod驱动怎么办?教你一招-如果没有可用的驱动,可以使用Zynq SoC PL端(可编程逻辑)的Pmod桥模块,它让我们能够在选用的开发板与Pmod端口之间建立正确的映射,然后开发我们自己的Zynq PS(处理系统)驱动。假如你仔细研究正规厂商所提供的Pmod驱动,你会发现这些驱动其实也是使用Pmod桥加上一个AXI I2C或者SPI组件所实现的。

CPLD的优势 FPGA的产生-FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD宏单元相似,但更容易配置,有更丰富的特性来提高性能,减少逻辑资源的浪费。

Xilinx滤波器IP核的延时问题-在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,但是阶数大小的选择要看是否满足自己的设计要求(例如衰减db是否满足要求)。同时,生成的滤波器抽头系数的值是与自己设计滤波器的各种参数确定的,如数据采样速率,通带截止频率、阻带起始频率(低通)、滤波器类型等。