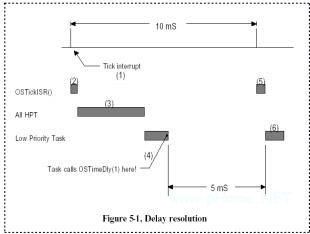

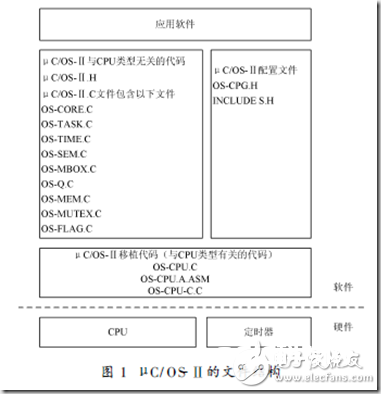

uCOSii的移植过程详解-产生时钟节拍的定时中断来自微控制器内部, 但并非来自V2 内核内部, 可以用实时时钟产生定时中断,也可以用片内的外设模块定时器单元来产生定时中断,这部分代码显然与硬件相关, 移植时要自己写

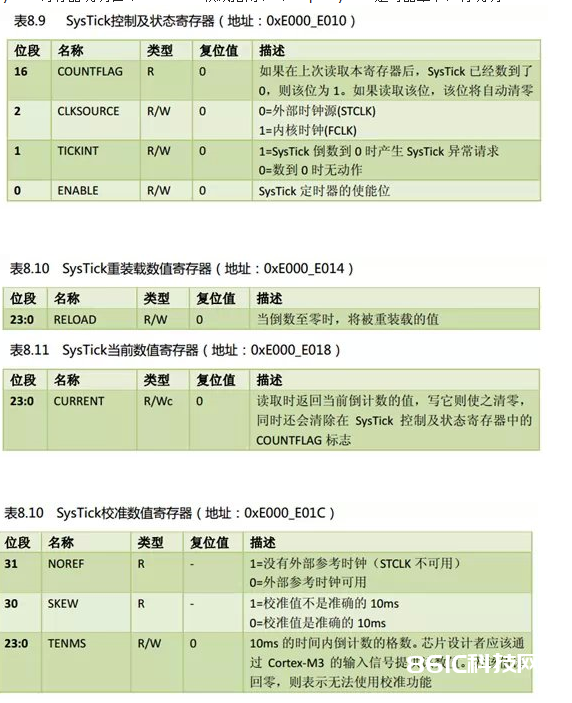

STM32知识:什么是SYSTICK 作用是什么-什么是 SYSTICK : 这是一个24位的系统节拍定时器system tick timer,SysTick,具有自动重载和溢出中断功能,所有基于Cortex_M3处理器的微控制器都可以由这个定时器获得一定的时间间隔。

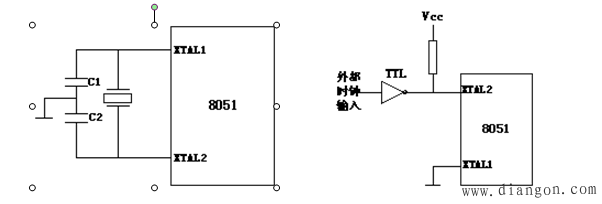

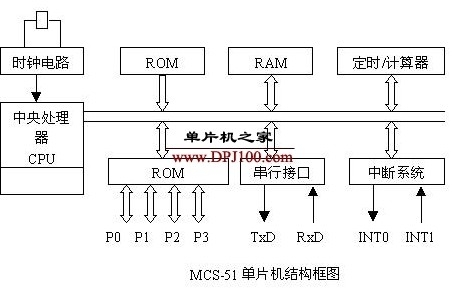

MCS-51单片机的时序单位的定义说明-我们把振荡脉冲的周期定义为节拍(为利便描述,用P表示),振荡脉冲经由二分频后即得到整个单片机工作系统的时钟信号,把时钟信号的周期定义为状态(用S表示),这样一个状态就有两个节拍,前半周期相应的节拍我们定义为1(P1),后半周期对应的节拍定义为2(P2)。

51单片机控制节拍产生程序设计-#include

sbitspeaker=P3^7;

unsignedcharDo=108;

unsignedcharbeat_H=(65536-62500)/256,beat_L()=(65536-62500)%256;

unsignedchartone_H=(65536-1908)/256,tone_L()=(65536-1908)%256;

chartimes,counts=5;

bitbeat_flag;