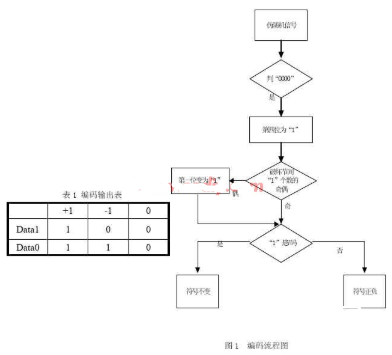

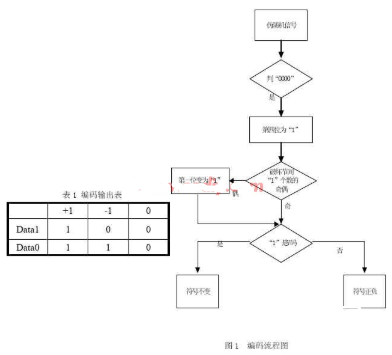

基于VHDL语言和可编程逻辑器件实现HDB3编译码器的设计-由于VHDL不能处理负电平,只能面向“1”、“0”两种状态,所以要对它的输出进行编码,如表1所示。编码的实现是根据HDB3编码原理把二进制码编码成两路单极性的码字输出,之后经过单双变换模块形成HDB3码。在编码过程中,要经过连0检测、破坏节判断、破坏节间“1”的个数判断、调整“1”的符号输出等步骤,编码部分可分为4个模块,编码流程如图1所示。

基于VHDL语言和可编程逻辑器件实现HDB3编译码器的设计-由于VHDL不能处理负电平,只能面向“1”、“0”两种状态,所以要对它的输出进行编码,如表1所示。编码的实现是根据HDB3编码原理把二进制码编码成两路单极性的码字输出,之后经过单双变换模块形成HDB3码。在编码过程中,要经过连0检测、破坏节判断、破坏节间“1”的个数判断、调整“1”的符号输出等步骤,编码部分可分为4个模块,编码流程如图1所示。