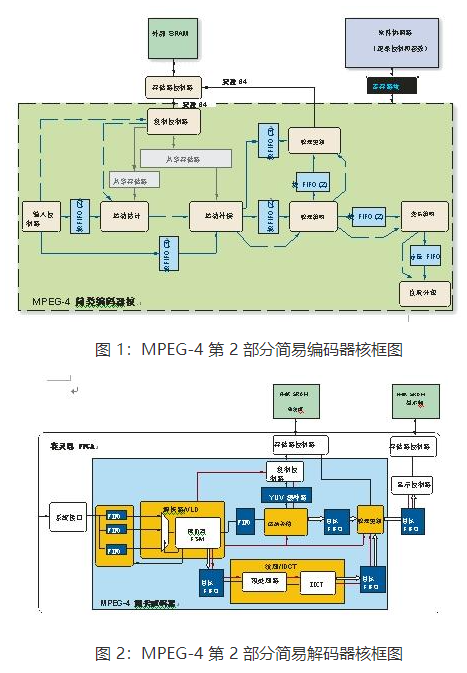

基于可编程逻辑器件实现MPEG-4简易编码器和解码器核的设计-您是否曾想在您的 FPGA 设计中使用先进的视频压缩技术,却发现实现起来太过复杂?现在您无需成为一名视频专家就能在您的系统中使用视频压缩。赛灵思新推出的 MPEG-4“ target=”_blank“》MPEG-4 编码器/解码器核可以帮助您满足视频压缩需求。

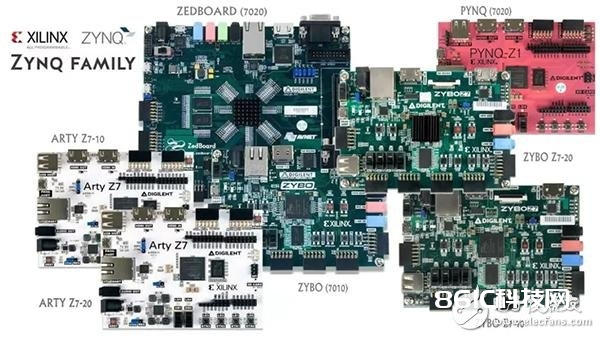

基于Zynq的HDMI传输和相关IP核介绍-为了简化编码解码器和PL之间的集成复杂度,这里介绍两个AVNET所开发的IP核,可通过Avnet GitHub下载( github.com/Avnet/hdl/tree/master/IP )。在图像处理链中,可以把它们放在处理链的最前端和最后端来连接外部的编解码器。

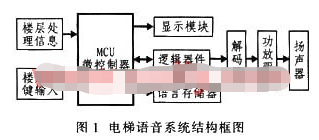

采用CPLD器件XC9572-VQ64芯片和MP3解码器实现语言播放系统的设计-语音系统是电梯不可缺少的部分,用于楼层报数、方向提示、报警告示、消防对讲以及广告宣传等。传统语音系统绝大多数采用语音器件存储和播放语音,但存在比如外围电路复杂、音质差、成本高、容量小以及语音不易更改等缺陷。鉴于此,设计了一款基于CPLD和VS1011E解码器的电梯语音系统。